ARTIX-7 FPGA

कोअर बोर्ड

AC7A200

मॉड्यूलवर सिस्टम

वापरकर्ता मॅन्युअल

आवृत्ती रेकॉर्ड

| आवृत्ती | तारीख | द्वारे सोडा | वर्णन |

| रेव्ह 1.0 | ५७४-५३७-८९०० | राहेल झोऊ | प्रथम प्रकाशन |

भाग 1: AC7A200 कोर बोर्ड परिचय

AC7A200 (कोर बोर्ड मॉडेल, खाली समान) FPGA कोर बोर्ड, हे XILINX च्या ARTIX-7 मालिका 100T XC7A200T-2FBG484I वर आधारित आहे. हा उच्च गती, उच्च बँडविड्थ आणि उच्च क्षमतेसह उच्च-कार्यक्षमता कोर बोर्ड आहे. हे हाय-स्पीड डेटा कम्युनिकेशन, व्हिडिओ इमेज प्रोसेसिंग, हाय-स्पीड डेटा संपादन इत्यादींसाठी योग्य आहे.

हा AC7A200 कोर बोर्ड MICRON च्या MT41J256M16HA-125 DDR3 चिपचे दोन तुकडे वापरतो, प्रत्येक DDR ची क्षमता 4Gbit आहे; दोन DDR चिप्स 32-बिट डेटा बस रुंदीमध्ये एकत्रित केल्या आहेत आणि FPGA आणि DDR3 मधील डेटा वाचन/लेखन बँडविड्थ 25Gb पर्यंत आहे; असे कॉन्फिगरेशन उच्च बँडविड्थ डेटा प्रोसेसिंगच्या गरजा पूर्ण करू शकते.

AC7A200 कोर बोर्ड 180V पातळीचे 3.3 मानक IO पोर्ट, 15V स्तराचे 1.5 मानक IO पोर्ट आणि GTP हायस्पीड RX/TX डिफरेंशियल सिग्नलच्या 4 जोड्या विस्तारित करतो. ज्या वापरकर्त्यांना भरपूर IO ची गरज आहे त्यांच्यासाठी हा कोर बोर्ड चांगला पर्याय असेल. शिवाय, FPGA चिप आणि इंटरफेसमधील रूटिंग समान लांबी आणि भिन्न प्रक्रिया आहे, आणि कोर बोर्ड आकार फक्त 2.36 इंच * 2.36 इंच आहे, जो दुय्यम विकासासाठी अतिशय योग्य आहे.

आकृती 1-1: AC7A200 कोर बोर्ड (समोर View)

आकृती 1-2: AC7A200 कोर बोर्ड (मागील View)

भाग 2: FPGA चिप

वर नमूद केल्याप्रमाणे, आम्ही वापरत असलेले FPGA मॉडेल XC7A200T-2FBG484I आहे, जे Xilinx च्या Artix-7 मालिकेशी संबंधित आहे. गती ग्रेड 2 आहे, आणि तापमान ग्रेड उद्योग ग्रेड आहे. हे मॉडेल 484 पिन असलेले FGG484 पॅकेज आहे. Xilinx ARTIX-7 FPGA चिप नामकरण नियम खाली दिले आहेत

आकृती 2-1: ARTIX-7 मालिकेची विशिष्ट चिप मॉडेल व्याख्या

आकृती 2-2: बोर्डवर FPGA चिप

FPGA चिप XC7A200T चे मुख्य पॅरामीटर्स खालीलप्रमाणे आहेत

| नाव | विशिष्ट मापदंड |

| लॉजिक सेल | 215360 |

| काप | ५७४-५३७-८९०० |

| CLB फ्लिप-फ्लॉप | 269200 |

| ब्लॉक रॅम (kb) | 13140 |

| डीएसपी स्लाइस | 740 |

| PCIe Gen2 | 1 |

| XADC | 1 XADC, 12bit, 1Mbps AD |

| GTP ट्रान्सीव्हर | 4 GTP, 6.6Gb/s कमाल |

| स्पीड ग्रेड | -2 |

| तापमान ग्रेड | औद्योगिक |

FPGA वीज पुरवठा प्रणाली

Artix-7 FPGA वीज पुरवठा VCCINT, VCCBRAM, VCCAUX, VCCO, VMGTAVCC आणि VMGTAVTT आहेत. VCCINT हा FPGA कोर पॉवर सप्लाय पिन आहे, जो 1.0V शी कनेक्ट करणे आवश्यक आहे; VCCBRAM हा FPGA ब्लॉक रॅमचा पॉवर सप्लाय पिन आहे, 1.0V शी कनेक्ट करा; VCCAUX FPGA सहाय्यक वीज पुरवठा पिन आहे, 1.8V कनेक्ट करा; VCCO हा खंड आहेtagBANK0, BANK13~16, BANK34~35 सह FPGA च्या प्रत्येक बँकेचा e. AC7A200 FPGA कोर बोर्डवर, BANK34 आणि BANK35 DDR3 शी जोडणे आवश्यक आहे, व्हॉल्यूमtagबँकेचे e कनेक्शन 1.5V आहे, आणि व्हॉल्यूमtagइतर BANK चा e 3.3V आहे. BANK15 आणि BANK16 चे VCCO LDO द्वारे समर्थित आहे, आणि LDO चिप बदलून बदलले जाऊ शकते. VMGTAVCC हा पुरवठा खंड आहेtagएफपीजीए अंतर्गत जीटीपी ट्रान्सीव्हरचा e, 1.0V शी जोडलेला; VMGTAVTT हे टर्मिनेशन व्हॉल्यूम आहेtagजीटीपी ट्रान्सीव्हरचा e, 1.2V शी जोडलेला आहे.

आर्टिक्स-7 FPGA प्रणालीसाठी पॉवर-अप अनुक्रम VCCINT, नंतर VCCBRAM, नंतर VCCAUX आणि शेवटी VCCO द्वारे पॉवर असणे आवश्यक आहे. VCCINT आणि VCCBRAM मध्ये समान व्हॉल्यूम असल्यासtage, ते एकाच वेळी चालू केले जाऊ शकतात. शक्ती ou क्रमtages उलट आहे. GTP ट्रान्सीव्हरचा पॉवर-अप क्रम VCCINT, नंतर VMGTAVCC, नंतर VMGTAVTT आहे. VCCINT आणि VMGTAVCC मध्ये समान व्हॉल्यूम असल्यासtage, ते एकाच वेळी चालू केले जाऊ शकतात. पॉवर-ऑफ अनुक्रम पॉवर-ऑन अनुक्रमाच्या अगदी उलट आहे.

भाग 3: सक्रिय विभेदक क्रिस्टल

AC7A200 कोर बोर्ड दोन Sitime सक्रिय विभेदक क्रिस्टल्सने सुसज्ज आहे, एक 200MHz आहे, मॉडेल SiT9102-200.00MHz आहे, FPGA साठी सिस्टम मुख्य घड्याळ आहे आणि DDR3 नियंत्रण घड्याळ तयार करण्यासाठी वापरले जाते; दुसरे 125MHz आहे, मॉडेल SiT9102 -125MHz आहे, GTP ट्रान्सीव्हर्ससाठी संदर्भ घड्याळ इनपुट.

भाग 3.1: 200Mhz सक्रिय विभेदक घड्याळ

आकृती 1-3 मधील G1 हे 200M सक्रिय विभेदक क्रिस्टल आहे जे डेव्हलपमेंट बोर्ड सिस्टम क्लॉक स्त्रोत प्रदान करते. क्रिस्टल आउटपुट FPGA च्या BANK34 ग्लोबल क्लॉक पिन MRCC (R4 आणि T4) शी जोडलेले आहे. हे 200Mhz भिन्न घड्याळ FPGA मध्ये वापरकर्ता तर्क चालविण्यासाठी वापरले जाऊ शकते. वापरकर्ते वेगवेगळ्या फ्रिक्वेन्सीची घड्याळे निर्माण करण्यासाठी FPGA मध्ये PLL आणि DCM कॉन्फिगर करू शकतात.

आकृती 3-1: 200Mhz सक्रिय विभेदक क्रिस्टल योजनाबद्ध

आकृती 3-2: कोर बोर्डवर 200Mhz सक्रिय विभेदक क्रिस्टल

200Mhz विभेदक घड्याळ पिन असाइनमेंट

| सिग्नलचे नाव | FPGA पिन |

| SYS_CLK_P | R4 |

| SYS_CLK_N | T4 |

भाग 3.2: 125MHz सक्रिय विभेदक क्रिस्टल

आकृती 2-3 मधील G3 हे 125MHz सक्रिय विभेदक क्रिस्टल आहे, जे FPGA अंतर्गत GTP मॉड्यूलला प्रदान केलेले संदर्भ इनपुट घड्याळ आहे. क्रिस्टल आउटपुट FPGA च्या GTP BANK216 घड्याळ पिन MGTREFCLK0P (F6) आणि MGTREFCLK0N (E6) शी जोडलेले आहे.

आकृती 3-3: 125MHz सक्रिय विभेदक क्रिस्टल योजनाबद्ध

आकृती 3-4: कोर बोर्डवर 125MHz सक्रिय विभेदक क्रिस्टल

125MHz विभेदक घड्याळ पिन असाइनमेंट

| निव्वळ नाव | FPGA पिन |

| MGT_CLK0_P | F6 |

| MGT_CLK0_N | E6 |

भाग 4: DDR3 DRAM

FPGA कोर बोर्ड AC7A200 दोन मायक्रॉन 4Gbit (512MB) DDR3 चिप्स (संपूर्णपणे 8Gbit) सुसज्ज आहे, मॉडेल MT41J256M16HA-125 (MT41K256M16HA-125 शी सुसंगत) आहे. DDR3 SDRAM ची कमाल ऑपरेटिंग गती 400MHz (डेटा दर 800Mbps) आहे. DDR3 मेमरी सिस्टीम FPGA च्या BANK 34 आणि BANK35 च्या मेमरी इंटरफेसशी थेट जोडलेली आहे. DDR3 SDRAM चे विशिष्ट कॉन्फिगरेशन तक्ता 4-1 मध्ये दर्शविले आहे.

| बिट क्रमांक | चिप मॉडेल | क्षमता | कारखाना |

| U5, U6 | MT41J256M16HA-125 | 256M x 16bit | मायक्रोन |

तक्ता 4-1: DDR3 SDRAM कॉन्फिगरेशन

DDR3 च्या हार्डवेअर डिझाइनसाठी सिग्नल अखंडतेचा काटेकोरपणे विचार करणे आवश्यक आहे. DDR3 चे हाय-स्पीड आणि स्थिर ऑपरेशन सुनिश्चित करण्यासाठी आम्ही सर्किट डिझाइन आणि पीसीबी डिझाइनमध्ये जुळणारे प्रतिरोधक/टर्मिनल प्रतिरोध, ट्रेस प्रतिबाधा नियंत्रण आणि ट्रेस लांबी नियंत्रण यांचा पूर्णपणे विचार केला आहे. आकृती 4-1 मध्ये DDR3 DRAM चे हार्डवेअर कनेक्शन तपशीलवार आहे

आकृती 4-1: DDR3 DRAM योजनाबद्ध

आकृती 4-2: कोर बोर्डवर DDR3

DDR3 DRAM पिन असाइनमेंट:

| निव्वळ नाव | FPGA पिन नाव | FPGA P/N |

| DDR3_DQS0_P | IO_L3P_T0_DQS_AD5P_35 | E1 |

| DDR3_DQS0_N | IO_L3N_T0_DQS_AD5N_35 | D1 |

| DDR3_DQS1_P | IO_L9P_T1_DQS_AD7P_35 | K2 |

| DDR3_DQS1_N | IO_L9N_T1_DQS_AD7N_35 | J2 |

| DDR3_DQS2_P | IO_L15P_T2_DQS_35 | M1 |

| DDR3_DQS2_N | IO_L15N_T2_DQS_35 | L1 |

| DDR3_DQS3_P | IO_L21P_T3_DQS_35 | P5 |

| DDR3_DQS3_N | IO_L21N_T3_DQS_35 | P4 |

| DDR3_DQ[0] | IO_L2P_T0_AD12P_35 | C2 |

| DDR3_DQ [१] | IO_L5P_T0_AD13P_35 | G1 |

| DDR3_DQ [१] | IO_L1N_T0_AD4N_35 | A1 |

| DDR3_DQ [१] | IO_L6P_T0_35 | F3 |

| DDR3_DQ [१] | IO_L2N_T0_AD12N_35 | B2 |

| DDR3_DQ [१] | IO_L5N_T0_AD13N_35 | F1 |

| DDR3_DQ [१] | IO_L1P_T0_AD4P_35 | B1 |

| DDR3_DQ [१] | IO_L4P_T0_35 | E2 |

| DDR3_DQ [१] | IO_L11P_T1_SRCC_35 | H3 |

| DDR3_DQ [१] | IO_L11N_T1_SRCC_35 | G3 |

| DDR3_DQ [१] | IO_L8P_T1_AD14P_35 | H2 |

| DDR3_DQ [१] | IO_L10N_T1_AD15N_35 | H5 |

| DDR3_DQ [१] | IO_L7N_T1_AD6N_35 | J1 |

| DDR3_DQ [१] | IO_L10P_T1_AD15P_35 | J5 |

| DDR3_DQ [१] | IO_L7P_T1_AD6P_35 | K1 |

| DDR3_DQ [१] | IO_L12P_T1_MRCC_35 | H4 |

| DDR3_DQ [१] | IO_L18N_T2_35 | L4 |

| DDR3_DQ [१] | IO_L16P_T2_35 | M3 |

| DDR3_DQ [१] | IO_L14P_T2_SRCC_35 | L3 |

| DDR3_DQ [१] | IO_L17N_T2_35 | J6 |

| DDR3_DQ [१] | IO_L14N_T2_SRCC_35 | K3 |

| DDR3_DQ [१] | IO_L17P_T2_35 | K6 |

| DDR3_DQ [१] | IO_L13N_T2_MRCC_35 | J4 |

| DDR3_DQ [१] | IO_L18P_T2_35 | L5 |

| DDR3_DQ [१] | IO_L20N_T3_35 | P1 |

| DDR3_DQ [१] | IO_L19P_T3_35 | N4 |

| DDR3_DQ [१] | IO_L20P_T3_35 | R1 |

| DDR3_DQ [१] | IO_L22N_T3_35 | N2 |

| DDR3_DQ [१] | IO_L23P_T3_35 | M6 |

| DDR3_DQ [१] | IO_L24N_T3_35 | N5 |

| DDR3_DQ [१] | IO_L24P_T3_35 | P6 |

| DDR3_DQ [१] | IO_L22P_T3_35 | P2 |

| DDR3_DM0 | IO_L4N_T0_35 | D2 |

| DDR3_DM1 | IO_L8N_T1_AD14N_35 | G2 |

| DDR3_DM2 | IO_L16N_T2_35 | M2 |

| DDR3_DM3 | IO_L23N_T3_35 | M5 |

| DDR3_A[0] | IO_L11N_T1_SRCC_34 | AA4 |

| DDR3_A[1] | IO_L8N_T1_34 | AB2 |

| DDR3_A[2] | IO_L10P_T1_34 | AA5 |

| DDR3_A[3] | IO_L10N_T1_34 | AB5 |

| DDR3_A[4] | IO_L7N_T1_34 | AB1 |

| DDR3_A[5] | IO_L6P_T0_34 | U3 |

| DDR3_A[6] | IO_L5P_T0_34 | W1 |

| DDR3_A[7] | IO_L1P_T0_34 | T1 |

| DDR3_A[8] | IO_L2N_T0_34 | V2 |

| DDR3_A[9] | IO_L2P_T0_34 | U2 |

| DDR3_A[10] | IO_L5N_T0_34 | Y1 |

| DDR3_A[11] | IO_L4P_T0_34 | W2 |

| DDR3_A[12] | IO_L4N_T0_34 | Y2 |

| DDR3_A[13] | IO_L1N_T0_34 | U1 |

| DDR3_A[14] | IO_L6N_T0_VREF_34 | V3 |

| DDR3_BA[0] | IO_L9N_T1_DQS_34 | AA3 |

| DDR3_BA[1] | IO_L9P_T1_DQS_34 | Y3 |

| DDR3_BA[2] | IO_L11P_T1_SRCC_34 | Y4 |

| DDR3_S0 | IO_L8P_T1_34 | AB3 |

| DDR3_RAS | IO_L12P_T1_MRCC_34 | V4 |

| DDR3_CAS | IO_L12N_T1_MRCC_34 | W4 |

| DDR3_WE | IO_L7P_T1_34 | AA1 |

| DDR3_ODT | IO_L14N_T2_SRCC_34 | U5 |

| DDR3_RESET | IO_L15P_T2_DQS_34 | W6 |

| DDR3_CLK_P | IO_L3P_T0_DQS_34 | R3 |

| DDR3_CLK_N | IO_L3N_T0_DQS_34 | R2 |

| DDR3_CKE | IO_L14P_T2_SRCC_34 | T5 |

भाग 5: QSPI फ्लॅश

FPGA कोर बोर्ड AC7A200 एक 128Mbit QSPI फ्लॅशने सुसज्ज आहे आणि मॉडेल N25Q128 आहे, जे 3.3V CMOS व्हॉल्यूम वापरतेtage मानक. QSPI FLASH च्या नॉन-अस्थिर स्वरूपामुळे, सिस्टमची बूट प्रतिमा संग्रहित करण्यासाठी ते सिस्टमसाठी बूट उपकरण म्हणून वापरले जाऊ शकते. या प्रतिमांमध्ये प्रामुख्याने FPGA बिट समाविष्ट आहे files, ARM ऍप्लिकेशन कोड, सॉफ्ट कोअर ऍप्लिकेशन कोड आणि इतर वापरकर्ता डेटा files SPI FLASH चे विशिष्ट मॉडेल्स आणि संबंधित पॅरामीटर्स तक्ता 5-1 मध्ये दर्शविले आहेत.

| स्थिती | मॉडेल | क्षमता | कारखाना |

| U8 | N25Q128 | 128M बिट | न्युमोनीक्स |

तक्ता 5-1: QSPI फ्लॅश तपशील

QSPI FLASH FPGA चिपच्या BANK0 आणि BANK14 च्या समर्पित पिनशी जोडलेले आहे. घड्याळाची पिन BANK0 च्या CCLK0 शी जोडलेली आहे, आणि इतर डेटा आणि चिप निवडक सिग्नल अनुक्रमे BANK00 च्या D03~D14 आणि FCS पिनशी जोडलेले आहेत. आकृती 5-1 QSPI फ्लॅशचे हार्डवेअर कनेक्शन दाखवते.

आकृती 5-1: QSPI फ्लॅश योजनाबद्ध

QSPI फ्लॅश पिन असाइनमेंट:

| निव्वळ नाव | FPGA पिन नाव | FPGA P/N |

| QSPI_CLK | CCLK_0 | L12 |

| QSPI_CS | IO_L6P_T0_FCS_B_14 | T19 |

| QSPI_DQ0 | IO_L1P_T0_D00_MOSI_14 | P22 |

| QSPI_DQ1 | IO_L1N_T0_D01_DIN_14 | R22 |

| QSPI_DQ2 | IO_L2P_T0_D02_14 | P21 |

| QSPI_DQ3 | IO_L2N_T0_D03_14 | R21 |

आकृती 5-2: कोर बोर्डवर QSPI फ्लॅश

भाग 6: कोर बोर्डवर एलईडी लाइट

AC3A7 FPGA कोर बोर्डवर 200 लाल LED दिवे आहेत, त्यापैकी एक पॉवर इंडिकेटर लाइट (PWR), एक कॉन्फिगरेशन LED लाइट (DONE) आहे आणि एक वापरकर्ता LED लाइट आहे. जेव्हा कोर बोर्ड चालविला जातो, तेव्हा पॉवर इंडिकेटर प्रकाशित होईल; जेव्हा FPGA कॉन्फिगर केले जाते, तेव्हा कॉन्फिगरेशन LED प्रकाशित होईल. वापरकर्ता LED लाइट BANK34 च्या IO शी जोडलेला आहे, वापरकर्ता प्रोग्रामद्वारे प्रकाश चालू आणि बंद करू शकतो. जेव्हा IO voltage वापरकर्त्याशी कनेक्ट केलेले एलईडी उच्च आहे, वापरकर्ता एलईडी प्रकाशित आहे. जेव्हा कनेक्शन IO voltage कमी आहे, वापरकर्ता LED विझवला जाईल. एलईडी लाईट हार्डवेअर कनेक्शनची योजनाबद्ध आकृती आकृती 6-1 मध्ये दर्शविली आहे:

आकृती 6-1: कोर बोर्ड योजनाबद्ध वर एलईडी दिवे

आकृती 6-2: कोर बोर्डवर एलईडी दिवे

वापरकर्ता LEDs पिन असाइनमेंट

| सिग्नलचे नाव | FPGA पिन नाव | FPGA पिन क्रमांक | वर्णन |

| LED1 | IO_L15N_T2_DQS_34 | W5 | वापरकर्ता LED |

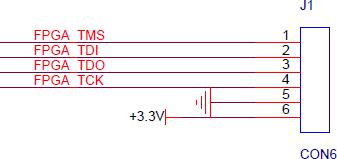

भाग 7: जेTAG इंटरफेस

जेTAG चाचणी सॉकेट J1 जे साठी AC7A200 कोर बोर्डवर आरक्षित आहेTAG जेव्हा कोर बोर्ड एकटा वापरला जातो तेव्हा डाउनलोड आणि डीबगिंग. आकृती 7-1 J चा योजनाबद्ध भाग आहेTAG पोर्ट, ज्यामध्ये TMS, TDI, TDO, TCK समाविष्ट आहे. , GND, +3.3V हे सहा सिग्नल.

आकृती 7-1: जेTAG इंटरफेस योजनाबद्ध

जेTAG AC1A7 FPGA कोर बोर्डवरील इंटरफेस J200 6-पिन 2.54mm पिच सिंगल-रो टेस्ट होल वापरतो. जर तुम्हाला जेTAG कोर बोर्डवर डीबग करण्यासाठी कनेक्टर, तुम्हाला 6-पिन सिंगल-रो पिन हेडर सोल्डर करणे आवश्यक आहे.

आकृती 7-2 जे दाखवतेTAG AC1A7 FPGA कोर बोर्डवर J200 इंटरफेस.

आकृती 7-2 जेTAG कोर बोर्डवर इंटरफेस

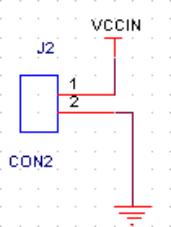

भाग 8: कोर बोर्डवर पॉवर इंटरफेस

AC7A200 FPGA कोर बोर्ड एकट्याने कार्य करण्यासाठी, कोर बोर्ड 2-पिन पॉवर सप्लाय इंटरफेस J2 राखीव आहे. जर वापरकर्त्याला कोर बोर्डचे कार्य स्वतंत्रपणे डीबग करायचे असेल (कॅरियर बोर्डशिवाय), तर बाह्य डिव्हाइसला कोर बोर्डला वीज पुरवण्यासाठी +5V प्रदान करणे आवश्यक आहे.

आकृती 8-1: कोअर बोर्डवर पॉवर इंटरफेस योजनाबद्ध

आकृती 8-2: कोअर बोर्डवर पॉवर इंटरफेस

भाग 9: बोर्ड टू बोर्ड कनेक्टर्स पिन असाइनमेंट

कोर बोर्डमध्ये एकूण चार हाय-स्पीड बोर्ड ते बोर्ड कनेक्टर आहेत.

कोर बोर्ड कॅरियर बोर्डला जोडण्यासाठी चार 80-पिन इंटर-बोर्ड कनेक्टर वापरतो. FPGA चे IO पोर्ट चार कनेक्टर्सना विभेदक मार्गाने जोडलेले आहे. कनेक्टर्सचे पिन स्पेसिंग 0.5 मिमी आहे, हाय-स्पीड डेटा कम्युनिकेशनसाठी कॅरियर बोर्डवर बोर्ड टू बोर्ड कनेक्टर्स घाला.

बोर्ड टू बोर्ड कनेक्टर्स CON1

80-पिन बोर्ड टू बोर्ड कनेक्टर्स CON1, जे VCCIN पॉवर सप्लाय (+5V) शी जोडण्यासाठी वापरले जातात आणि वाहक बोर्डवर ग्राउंड केले जातात, FPGA चे सामान्य IOs वाढवतात. येथे हे लक्षात घेतले पाहिजे की CON15 चे 1 पिन BANK34 च्या IO पोर्टशी जोडलेले आहेत, कारण BANK34 कनेक्शन DDR3 शी जोडलेले आहे. म्हणून, खंडtagया BANK34 च्या सर्व IO चे मानक 1.5V आहे.

बोर्ड कनेक्टर्स CON1 ला बोर्डचे पिन असाइनमेंट

| CON1 पिन |

नेट नाव |

FPGA पिन |

खंडtage पातळी |

CON1 पिन |

नेट नाव |

FPGA पिन |

खंडtage पातळी |

| पिन 1 | VCCIN | – | +5V | पिन 2 | VCCIN | – | +5V |

| पिन 3 | VCCIN | – | +5V | पिन 4 | VCCIN | – | +5V |

| पिन 5 | VCCIN | – | +5V | पिन 6 | VCCIN | – | +5V |

| पिन 7 | VCCIN | – | +5V | पिन 8 | VCCIN | – | +5V |

| पिन 9 | GND | – | ग्राउंड | पिन 10 | GND | – | ग्राउंड |

| पिन 11 | NC | – | NC | पिन 12 | NC | – | NC |

| पिन 13 | NC | – | NC | पिन 14 | NC | – | NC |

| पिन 15 | NC | – | NC | पिन 16 | B13_L4_P | AA15 | 3.3V |

| पिन 17 | NC | – | NC | पिन 18 | B13_L4_N | AB15 | 3.3V |

| पिन 19 | GND | – | ग्राउंड | पिन 20 | GND | – | ग्राउंड |

| पिन 21 | B13_L5_P | Y13 | 3.3V | पिन 22 | B13_L1_P | Y16 | 3.3V |

| पिन 23 | B13_L5_N | AA14 | 3.3V | पिन 24 | B13_L1_N | AA16 | 3.3V |

| पिन 25 | B13_L7_P | AB11 | 3.3V | पिन 26 | B13_L2_P | AB16 | 3.3V |

| पिन 27 | B13_L7_P | AB12 | 3.3V | पिन 28 | B13_L2_N | AB17 | 3.3V |

| पिन 29 | GND | – | ग्राउंड | पिन 30 | GND | – | ग्राउंड |

| पिन 31 | B13_L3_P | AA13 | 3.3V | पिन 32 | B13_L6_P | W14 | 3.3V |

| पिन 33 | B13_L3_N | AB13 | 3.3V | पिन 34 | B13_L6_N | Y14 | 3.3V |

| पिन 35 | B34_L23_P | Y8 | 1.5V | पिन 36 | B34_L20_P | AB7 | 1.5V |

| पिन 37 | B34_L23_N | Y7 | 1.5V | पिन 38 | B34_L20_N | AB6 | 1.5V |

| पिन 39 | GND | – | ग्राउंड | पिन 40 | GND | – | ग्राउंड |

| पिन 41 | B34_L18_N | AA6 | 1.5V | पिन 42 | B34_L21_N | V8 | 1.5V |

| पिन 43 | B34_L18_P | Y6 | 1.5V | पिन 44 | B34_L21_P | V9 | 1.5V |

| पिन 45 | B34_L19_P | V7 | 1.5V | पिन 46 | B34_L22_P | AA8 | 1.5V |

| पिन 47 | B34_L19_N | W7 | 1.5V | पिन 48 | B34_L22_N | AB8 | 1.5V |

| पिन 49 | GND | – | ग्राउंड | पिन 50 | GND | – | ग्राउंड |

| पिन 51 | XADC_VN | M9 | ॲनालॉग | पिन 52 | NC | ||

| पिन 53 | XADC_VP | L10 | ॲनालॉग | पिन 54 | B34_L25 | U7 | 1.5V |

| पिन 55 | NC | – | NC | पिन 56 | B34_L24_P | W9 | 1.5V |

| पिन 57 | NC | – | NC | पिन 58 | B34_L24_N | Y9 | 1.5V |

| पिन 59 | GND | – | ग्राउंड | पिन 60 | GND | – | ग्राउंड |

| पिन 61 | B16_L1_N | F14 | 3.3V | पिन 62 | NC | – | NC |

| पिन 63 | B16_L1_P | F13 | 3.3V | पिन 64 | NC | – | NC |

| पिन 65 | B16_L4_N | E14 | 3.3V | पिन 66 | NC | – | NC |

| पिन 67 | B16_L4_P | E13 | 3.3V | पिन 68 | NC | – | NC |

| पिन 69 | GND | – | ग्राउंड | पिन 70 | GND | – | ग्राउंड |

| पिन 71 | B16_L6_N | D15 | 3.3V | पिन 72 | NC | – | NC |

| पिन 73 | B16_L6_P | D14 | 3.3V | पिन 74 | NC | – | NC |

| पिन 75 | B16_L8_P | C13 | 3.3V | पिन 76 | NC | – | NC |

| पिन 77 | B16_L8_N | B13 | 3.3V | पिन 78 | NC | – | NC |

| पिन 79 | NC | – | NC | पिन 80 | NC | – | NC |

आकृती 9-1: कोअर बोर्डवर बोर्ड टू बोर्ड कनेक्टर्स CON1

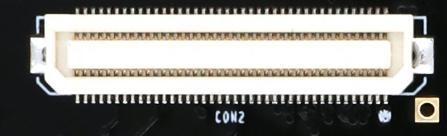

बोर्ड टू बोर्ड कनेक्टर्स CON2

80-पिन महिला कनेक्शन शीर्षलेख CON2 चा वापर FPGA च्या BANK13 आणि BANK14 चा सामान्य IO वाढवण्यासाठी केला जातो. खंडtagदोन्ही बँकांचे e मानक 3.3V आहेत.

बोर्ड कनेक्टर्स CON2 ला बोर्डचे पिन असाइनमेंट

| CON2 पिन |

नेट नाव |

FPGA पिन |

खंडtage पातळी |

CON2 पिन |

नेट नाव |

FPGA पिन |

खंडtage पातळी |

| पिन 1 | B13_L16_P | W15 | 3.3V | पिन 2 | B14_L16_P | V17 | 3.3V |

| पिन 3 | B13_L16_N | W16 | 3.3V | पिन 4 | B14_L16_N | W17 | 3.3V |

| पिन 5 | B13_L15_P | T14 | 3.3V | पिन 6 | B13_L14_P | U15 | 3.3V |

| पिन 7 | B13_L15_N | T15 | 3.3V | पिन 8 | B13_L14_N | V15 | 3.3V |

| पिन 9 | GND | – | ग्राउंड | पिन 10 | GND | – | ग्राउंड |

| पिन 11 | B13_L13_P | V13 | 3.3V | पिन 12 | B14_L10_P | AB21 | 3.3V |

| पिन 13 | B13_L13_N | V14 | 3.3V | पिन 14 | B14_L10_N | AB22 | 3.3V |

| पिन 15 | B13_L12_P | W11 | 3.3V | पिन 16 | B14_L8_N | AA21 | 3.3V |

| पिन 17 | B13_L12_N | W12 | 3.3V | पिन 18 | B14_L8_P | AA20 | 3.3V |

| पिन 19 | GND | – | ग्राउंड | पिन 20 | GND | – | ग्राउंड |

| पिन 21 | B13_L11_P | Y11 | 3.3V | पिन 22 | B14_L15_N | AB20 | 3.3V |

| पिन 23 | B13_L11_N | Y12 | 3.3V | पिन 24 | B14_L15_P | AA19 | 3.3V |

| पिन 25 | B13_L10_P | V10 | 3.3V | पिन 26 | B14_L17_P | AA18 | 3.3V |

| पिन 27 | B13_L10_N | W10 | 3.3V | पिन 28 | B14_L17_N | AB18 | 3.3V |

| पिन 29 | GND | – | ग्राउंड | पिन 30 | GND | – | ग्राउंड |

| पिन 31 | B13_L9_N | AA11 | 3.3V | पिन 32 | B14_L6_N | T20 | 3.3V |

| पिन 33 | B13_L9_P | AA10 | 3.3V | पिन 34 | B13_IO0 | Y17 | 3.3V |

| पिन 35 | B13_L8_N | AB10 | 3.3V | पिन 36 | B14_L7_N | W22 | 3.3V |

| पिन 37 | B13_L8_P | AA9 | 3.3V | पिन 38 | B14_L7_P | W21 | 3.3V |

| पिन 39 | GND | – | ग्राउंड | पिन 40 | GND | – | ग्राउंड |

| पिन 41 | B14_L11_N | V20 | 3.3V | पिन 42 | B14_L4_P | T21 | 3.3V |

| पिन 43 | B14_L11_P | U20 | 3.3V | पिन 44 | B14_L4_N | U21 | 3.3V |

| पिन 45 | B14_L14_N | V19 | 3.3V | पिन 46 | B14_L9_P | Y21 | 3.3V |

| पिन 47 | B14_L14_P | V18 | 3.3V | पिन 48 | B14_L9_N | Y22 | 3.3V |

| पिन 49 | GND | – | ग्राउंड | पिन 50 | GND | – | ग्राउंड |

| पिन 51 | B14_L5_N | R19 | 3.3V | पिन 52 | B14_L12_N | W20 | 3.3V |

| पिन 53 | B14_L5_P | P19 | 3.3V | पिन 54 | B14_L12_P | W19 | 3.3V |

| पिन 55 | B14_L18_N | U18 | 3.3V | पिन 56 | B14_L13_N | Y19 | 3.3V |

| पिन 57 | B14_L18_P | U17 | 3.3V | पिन 58 | B14_L13_P | Y18 | 3.3V |

| पिन 59 | GND | – | ग्राउंड | पिन 60 | GND | – | ग्राउंड |

| पिन 61 | B13_L17_P | T16 | 3.3V | पिन 62 | B14_L3_N | V22 | 3.3V |

| पिन 63 | B13_L17_N | U16 | 3.3V | पिन 64 | B14_L3_P | U22 | 3.3V |

| पिन 65 | B14_L21_N | P17 | 3.3V | पिन 66 | B14_L20_N | T18 | 3.3V |

| पिन 67 | B14_L21_P | N17 | 3.3V | पिन 68 | B14_L20_P | R18 | 3.3V |

| पिन 69 | GND | – | ग्राउंड | पिन 70 | GND | – | ग्राउंड |

| पिन 71 | B14_L22_P | P15 | 3.3V | पिन 72 | B14_L19_N | R14 | 3.3V |

| पिन 73 | B14_L22_N | R16 | 3.3V | पिन 74 | B14_L19_P | P14 | 3.3V |

| पिन 75 | B14_L24_N | R17 | 3.3V | पिन 76 | B14_L23_P | N13 | 3.3V |

| पिन 77 | B14_L24_P | P16 | 3.3V | पिन 78 | B14_L23_N | N14 | 3.3V |

| पिन 79 | B14_IO0 | P20 | 3.3V | पिन 80 | B14_IO25 | N15 | 3.3V |

आकृती 9-2: कोअर बोर्डवर बोर्ड टू बोर्ड कनेक्टर्स CON2

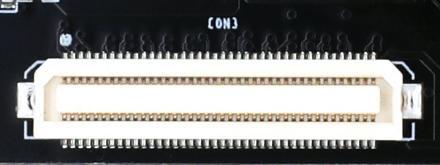

बोर्ड टू बोर्ड कनेक्टर्स CON3

80-पिन कनेक्टर CON3 चा वापर FPGA च्या BANK15 आणि BANK16 चा सामान्य IO वाढवण्यासाठी केला जातो. याशिवाय चार जेTAG CON3 कनेक्टरद्वारे सिग्नल देखील कॅरियर बोर्डशी जोडलेले आहेत. खंडtagBANK15 आणि BANK16 चे मानक LDO चिपद्वारे समायोजित केले जाऊ शकतात. डीफॉल्ट स्थापित LDO 3.3V आहे. तुम्हाला इतर मानक स्तर आउटपुट करायचे असल्यास, तुम्ही ते योग्य LDO ने बदलू शकता.

बोर्ड कनेक्टर्स CON3 ला बोर्डचे पिन असाइनमेंट

| CON3 पिन |

नेट नाव |

FPGA पिन |

खंडtage पातळी |

CON3 पिन |

नेट नाव |

FPGA पिन |

खंडtage पातळी |

| पिन 1 | B15_IO0 | J16 | 3.3V | पिन 2 | B15_IO25 | M17 | 3.3V |

| पिन 3 | B16_IO0 | F15 | 3.3V | पिन 4 | B16_IO25 | F21 | 3.3V |

| पिन 5 | B15_L4_P | G17 | 3.3V | पिन 6 | B16_L21_N | A21 | 3.3V |

| पिन 7 | B15_L4_N | G18 | 3.3V | पिन 8 | B16_L21_P | B21 | 3.3V |

| पिन 9 | GND | – | ग्राउंड | पिन 10 | GND | – | ग्राउंड |

| पिन 11 | B15_L2_P | G15 | 3.3V | पिन 12 | B16_L23_P | E21 | 3.3V |

| पिन 13 | B15_L2_N | G16 | 3.3V | पिन 14 | B16_L23_N | D21 | 3.3V |

| पिन 15 | B15_L12_P | J19 | 3.3V | पिन 16 | B16_L22_P | E22 | 3.3V |

| पिन 17 | B15_L12_N | H19 | 3.3V | पिन 18 | B16_L22_N | D22 | 3.3V |

| पिन 19 | GND | – | ग्राउंड | पिन 20 | GND | – | ग्राउंड |

| पिन 21 | B15_L11_P | J20 | 3.3V | पिन 22 | B16_L24_P | G21 | 3.3V |

| पिन 23 | B15_L11_N | J21 | 3.3V | पिन 24 | B16_L24_N | G22 | 3.3V |

| पिन 25 | B15_L1_N | G13 | 3.3V | पिन 26 | B15_L8_N | G20 | 3.3V |

| पिन 27 | B15_L1_P | H13 | 3.3V | पिन 28 | B15_L8_P | H20 | 3.3V |

| पिन 29 | GND | – | ग्राउंड | पिन 30 | GND | – | ग्राउंड |

| पिन 31 | B15_L5_P | J15 | 3.3V | पिन 32 | B15_L7_N | H22 | 3.3V |

| पिन 33 | B15_L5_N | H15 | 3.3V | पिन 34 | B15_L7_P | J22 | 3.3V |

| पिन 35 | B15_L3_N | H14 | 3.3V | पिन 36 | B15_L9_P | K21 | 3.3V |

| पिन 37 | B15_L3_P | J14 | 3.3V | पिन 38 | B15_L9_N | K22 | 3.3V |

| पिन 39 | GND | – | ग्राउंड | पिन 40 | GND | – | ग्राउंड |

| पिन 41 | B15_L19_P | K13 | 3.3V | पिन 42 | B15_L15_N | M22 | 3.3V |

| पिन 43 | B15_L19_N | K14 | 3.3V | पिन 44 | B15_L15_P | N22 | 3.3V |

| पिन 45 | B15_L20_P | M13 | 3.3V | पिन 46 | B15_L6_N | H18 | 3.3V |

| पिन 47 | B15_L20_N | L13 | 3.3V | पिन 48 | B15_L6_P | H17 | 3.3V |

| पिन 49 | GND | – | ग्राउंड | पिन 50 | GND | – | ग्राउंड |

| पिन 51 | B15_L14_P | L19 | 3.3V | पिन 52 | B15_L13_N | K19 | 3.3V |

| पिन 53 | B15_L14_N | L20 | 3.3V | पिन 54 | B15_L13_P | K18 | 3.3V |

| पिन 55 | B15_L21_P | K17 | 3.3V | पिन 56 | B15_L10_P | M21 | 3.3V |

| पिन 57 | B15_L21_N | J17 | 3.3V | पिन 58 | B15_L10_N | L21 | 3.3V |

| पिन 59 | GND | – | ग्राउंड | पिन 60 | GND | – | ग्राउंड |

| पिन 61 | B15_L23_P | L16 | 3.3V | पिन 62 | B15_L18_P | N20 | 3.3V |

| पिन 63 | B15_L23_N | K16 | 3.3V | पिन 64 | B15_L18_N | M20 | 3.3V |

| पिन 65 | B15_L22_P | L14 | 3.3V | पिन 66 | B15_L17_N | N19 | 3.3V |

| पिन 67 | B15_L22_N | L15 | 3.3V | पिन 68 | B15_L17_P | N18 | 3.3V |

| पिन 69 | GND | – | ग्राउंड | पिन 70 | GND | – | ग्राउंड |

| पिन 71 | B15_L24_P | M15 | 3.3V | पिन 72 | B15_L16_P | M18 | 3.3V |

| पिन 73 | B15_L24_N | M16 | 3.3V | पिन 74 | B15_L16_N | L18 | 3.3V |

| पिन 75 | NC | – | पिन 76 | NC | – | ||

| पिन 77 | FPGA_TCK | V12 | 3.3V | पिन 78 | FPGA_TDI | R13 | 3.3V |

| पिन 79 | FPGA_TDO | U13 | 3.3V | पिन 80 | FPGA_TMS | T13 | 3.3V |

आकृती 9-3: कोअर बोर्डवर बोर्ड टू बोर्ड कनेक्टर्स CON3

बोर्ड टू बोर्ड कनेक्टर्स CON4

80-पिन कनेक्टर CON4 चा वापर सामान्य IO आणि GTP हाय-स्पीड डेटा आणि FPGA BANK16 चे घड्याळ सिग्नल वाढवण्यासाठी केला जातो. खंडtagBANK16 च्या IO पोर्टचे e मानक LDO चिपद्वारे समायोजित केले जाऊ शकते. डीफॉल्ट स्थापित LDO 3.3V आहे. जर वापरकर्त्याला इतर मानक स्तर आउटपुट करायचे असतील तर ते योग्य LDO द्वारे बदलले जाऊ शकते. GTP चा हाय-स्पीड डेटा आणि घड्याळ सिग्नल कोर बोर्डवर काटेकोरपणे भिन्न आहेत. डेटा लाइन्स लांबीच्या समान असतात आणि सिग्नल हस्तक्षेप टाळण्यासाठी विशिष्ट अंतराने ठेवतात.

बोर्ड कनेक्टर्स CON4 ला बोर्डचे पिन असाइनमेंट

| CON4 पिन |

नेट नाव |

FPGA पिन |

खंडtage पातळी |

CON4 पिन |

नेट नाव |

FPGA पिन |

खंडtage पातळी |

| पिन 1 | NC | – | – | पिन 2 | – | – | |

| पिन 3 | NC | – | – | पिन 4 | – | – | |

| पिन 5 | NC | – | – | पिन 6 | – | – | |

| पिन 7 | NC | – | – | पिन 8 | – | – | |

| पिन 9 | GND | – | ग्राउंड | पिन 10 | GND | – | ग्राउंड |

| पिन 11 | NC | – | – | पिन 12 | MGT_TX2_P | B6 | फरक |

| पिन 13 | NC | – | – | पिन 14 | MGT_TX2_N | A6 | फरक |

| पिन 15 | GND | – | ग्राउंड | पिन 16 | GND | – | ग्राउंड |

| पिन 17 | MGT_TX3_P | D7 | फरक | पिन 18 | MGT_RX2_P | B10 | फरक |

| पिन 19 | MGT_TX3_N | C7 | फरक | पिन 20 | MGT_RX2_N | A10 | फरक |

| पिन 21 | GND | – | ग्राउंड | पिन 22 | GND | – | ग्राउंड |

| पिन 23 | MGT_RX3_P | D9 | फरक | पिन 24 | MGT_TX0_P | B4 | फरक |

| पिन 25 | MGT_RX3_N | C9 | फरक | पिन 26 | MGT_TX0_N | A4 | फरक |

| पिन 27 | GND | – | ग्राउंड | पिन 28 | GND | – | ग्राउंड |

| पिन 29 | MGT_TX1_P | D5 | फरक | पिन 30 | MGT_RX0_P | B8 | फरक |

| पिन 31 | MGT_TX1_N | C5 | फरक | पिन 32 | MGT_RX0_N | A8 | फरक |

| पिन 33 | GND | – | ग्राउंड | पिन 34 | GND | – | ग्राउंड |

| पिन 35 | MGT_RX1_P | D11 | फरक | पिन 36 | MGT_CLK1_P | F10 | फरक |

| पिन 37 | MGT_RX1_N | C11 | फरक | पिन 38 | MGT_CLK1_N | E10 | फरक |

| पिन 39 | GND | – | ग्राउंड | पिन 40 | GND | – | ग्राउंड |

| पिन 41 | B16_L5_P | E16 | 3.3V | पिन 42 | B16_L2_P | F16 | 3.3V |

| पिन 43 | B16_L5_N | D16 | 3.3V | पिन 44 | B16_L2_N | E17 | 3.3V |

| पिन 45 | B16_L7_P | B15 | 3.3V | पिन 46 | B16_L3_P | C14 | 3.3V |

| पिन 47 | B16_L7_N | B16 | 3.3V | पिन 48 | B16_L3_N | C15 | 3.3V |

| पिन 49 | GND | – | ग्राउंड | पिन 50 | GND | – | ग्राउंड |

| पिन 51 | B16_L9_P | A15 | 3.3V | पिन 52 | B16_L10_P | A13 | 3.3V |

| पिन 53 | B16_L9_N | A16 | 3.3V | पिन 54 | B16_L10_N | A14 | 3.3V |

| पिन 55 | B16_L11_P | B17 | 3.3V | पिन 56 | B16_L12_P | D17 | 3.3V |

| पिन 57 | B16_L11_N | B18 | 3.3V | पिन 58 | B16_L12_N | C17 | 3.3V |

| पिन 59 | GND | – | ग्राउंड | पिन 60 | GND | – | ग्राउंड |

| पिन 61 | B16_L13_P | C18 | 3.3V | पिन 62 | B16_L14_P | E19 | 3.3V |

| पिन 63 | B16_L13_N | C19 | 3.3V | पिन 64 | B16_L14_N | D19 | 3.3V |

| पिन 65 | B16_L15_P | F18 | 3.3V | पिन 66 | B16_L16_P | B20 | 3.3V |

| पिन 67 | B16_L15_N | E18 | 3.3V | पिन 68 | B16_L16_N | A20 | 3.3V |

| पिन 69 | GND | – | ग्राउंड | पिन 70 | GND | – | ग्राउंड |

| पिन 71 | B16_L17_P | A18 | 3.3V | पिन 72 | B16_L18_P | F19 | 3.3V |

| पिन 73 | B16_L17_N | A19 | 3.3V | पिन 74 | B16_L18_N | F20 | 3.3V |

| पिन 75 | B16_L19_P | D20 | 3.3V | पिन 76 | B16_L20_P | C22 | 3.3V |

| पिन 77 | B16_L19_N | C20 | 3.3V | पिन 78 | B16_L20_N | B22 | 3.3V |

| पिन 79 | NC | – | पिन 80 | NC | – |

आकृती 9-4: कोअर बोर्डवर बोर्ड टू बोर्ड कनेक्टर्स CON4

भाग 10: वीज पुरवठा

AC7A200 FPGA कोर बोर्ड कॅरियर बोर्डद्वारे DC5V द्वारे समर्थित आहे आणि जेव्हा ते एकटे वापरले जाते तेव्हा ते मिनी USB इंटरफेसद्वारे समर्थित आहे. कृपया नुकसान टाळण्यासाठी मिनी यूएसबी आणि वाहक बोर्डाने एकाच वेळी वीजपुरवठा न करण्याची काळजी घ्या. बोर्डवरील वीज पुरवठा डिझाइन आकृती आकृती 10-1 मध्ये दर्शविली आहे.

आकृती 10-1: कोर बोर्ड योजनाबद्ध वर वीज पुरवठा

कोर बोर्ड +5V द्वारे समर्थित आहे आणि तीन DC/DC पॉवर सप्लाय चिप TLV3.3RGT द्वारे +1.5V, +1.8V, +1.0V, +62130V चार-मार्गी वीज पुरवठ्यामध्ये रूपांतरित केला जातो. +1.0V चा प्रवाह 6A पर्यंत असू शकतो आणि इतर तीन आउटपुट प्रवाह 3A पर्यंत असू शकतात. VCCIO एका LDOSPX3819M5-3-3 द्वारे व्युत्पन्न केले आहे. VCCIO प्रामुख्याने FPGA च्या BANK15 आणि BANK16 ला वीज पुरवठा करते. वापरकर्ते BANK15,16 चा IO वेगवेगळ्या व्हॉल्यूममध्ये बदलू शकतातtagई मानके त्यांची LDO चिप बदलून. 1.5V VTT आणि VREF व्हॉल्यूम व्युत्पन्न करतेtagTI च्या TPS3 द्वारे DDR51200 द्वारे आवश्यक आहे. GTP ट्रान्सीव्हरसाठी MGTAVTT आणि MGTAVCC चा 1.8V वीज पुरवठा TI च्या TPS74801 चिपद्वारे निर्माण केला जातो. प्रत्येक उर्जा वितरणाची कार्ये खालील सारणीमध्ये दर्शविली आहेत:

| वीज पुरवठा | कार्य |

| +1.0V | FPGA Core Voltage |

| +1.8V | FPGA सहाय्यक खंडtagई, TPS74801 वीज पुरवठा |

| +3.3V | FPGA चे Bank0, Bank13 आणि Bank14 चे VCCIO, QSIP फ्लॅश, क्लॉक क्रिस्टल |

| +1.5V | FPGA चे DDR3, Bank34 आणि Bank35 |

| VREF, VTT(+0.75V) | DDR3 |

| CCIP(+3.3V) | FPGA Bank15, Bank16 |

| MGTAVTT(+1.2V) | FPGA ची GTP ट्रान्सीव्हर बँक216 |

| MGTVCC(+1.0V) | FPGA ची GTP ट्रान्सीव्हर बँक216 |

आर्टिक्स-7 FPGA च्या पॉवर सप्लायला पॉवर-ऑन सीक्वेन्सची आवश्यकता असल्यामुळे, सर्किट डिझाइनमध्ये, आम्ही चिपच्या पॉवर आवश्यकतांनुसार डिझाइन केले आहे आणि पॉवर-ऑन 1.0V->1.8V->(1.5) आहे. V, 3.3V, VCCIO) आणि 1.0V-> MGTAVCC -> MGTAVTT, चिपचे सामान्य ऑपरेशन सुनिश्चित करण्यासाठी सर्किट डिझाइन.

AC7A200 FPGA कोर बोर्डवरील पॉवर सर्किट आकृती 10-2 मध्ये दर्शविले आहे:

आकृती 10-2: AC7A200 FPGA कोर बोर्डवर वीज पुरवठा

भाग 11: आकार परिमाण

आकृती 11-1: AC7A200 FPGA कोर बोर्ड (शीर्ष View)

आकृती 11-2: AC7A200 FPGA कोर बोर्ड (तळाशी View)

कागदपत्रे / संसाधने

|

ALINX AC7A200 ARTIX-7 FPGA विकास मंडळ [pdf] वापरकर्ता मॅन्युअल AC7A200 ARTIX-7 FPGA विकास मंडळ, AC7A200, ARTIX-7 FPGA विकास मंडळ, FPGA विकास मंडळ, विकास मंडळ, मंडळ |