AN3468

एक प्रकार 1/2 802.3 किंवा HDBaseT प्रकार 3 समर्थित डिझाइन करणे

PD702x0 आणि PD701x0 ICs वापरून डिव्हाइस फ्रंट-एंड

परिचय

ही ऍप्लिकेशन नोट IEEE® 802.3af, IEEE 802.3at, HDBaseT (PoH) आणि युनिव्हर्सल पॉवर ओव्हर इथरनेट (UPoE) ऍप्लिकेशन्ससाठी पॉवर ओव्हर इथरनेट (PoE) पॉवर्ड डिव्हाइस (PD) सिस्टम डिझाइन करण्यासाठी मार्गदर्शक तत्त्वे प्रदान करते. -एंड पीडी इंटिग्रेटेड सर्किट्स. खालील तक्त्यामध्ये मायक्रोचिप पीडी उत्पादनांच्या ऑफरची सूची आहे.

तक्ता 1. मायक्रोचिप चालित उपकरण उत्पादने ऑफरिंग

| भाग | प्रकार | पॅकेज | IEEE® 802.3af |

IEEE 802.3at |

HDBaseT (PoH) |

UPoE |

| PD70100 | समोरचे टोक | 3 मिमी × 4 मिमी 12L DFN | x | — | — | — |

| PD70101 | फ्रंट एंड + PWM | 5 मिमी × 5 मिमी 32L QFN | x | — | — | — |

| PD70200 | समोरचे टोक | 3 मिमी × 4 मिमी 12L DFN | x | x | — | — |

| PD70201 | फ्रंट एंड + PWM | 5 मिमी × 5 मिमी 32L QFN | x | x | — | — |

| PD70210 | समोरचे टोक | 4 मिमी × 5 मिमी 16L DFN | x | x | x | x |

| PD70210A | समोरचे टोक | 4 मिमी × 5 मिमी 16L DFN | x | x | x | x |

| PD70210AL | समोरचे टोक | 5 मिमी × 7 मिमी 38L QFN | x | x | x | x |

| PD70211 | फ्रंट एंड + PWM | 6 मिमी × 6 मिमी 36L QFN | x | x | x | x |

| PD70224 | आदर्श डायोड ब्रिज | 6 मिमी × 8 मिमी 40L QFN | x | x | x | x |

मायक्रोचिप स्टँडअलोन फ्रंट-एंड पीडी उपकरणे ऑफर करते ज्यांना उच्च PoE व्हॉल्यूम रूपांतरित करण्यासाठी बाह्य PWM IC आवश्यक आहेtage खाली नियमित पुरवठा खंडtage अनुप्रयोगाद्वारे वापरले जाते. याव्यतिरिक्त, मायक्रोचिप PD डिव्हाइसेस ऑफर करते जे उत्पादन पॅकेजमध्ये फ्रंट-एंड PD आणि PWM एकत्रित करतात. या ऍप्लिकेशन नोटची व्याप्ती मायक्रोचिप फ्रंट-एंड-ओन्ली उत्पादने (PD701x0 आणि PD702x0) वापरून PoE PD फ्रंटच्या डिझाइनचे वर्णन करणे आहे. या दस्तऐवजात मायक्रोचिपच्या पीडी उत्पादनांची प्रमुख वैशिष्ट्ये आणि कार्यांचे वर्णन देखील समाविष्ट आहे, थोडक्यातview PoE कार्यक्षमता, मानके आणि PoE PD डिझाइनसाठी मुख्य तांत्रिक बाबी.

फ्रंट-एंड PD उत्पादने आवश्यक शोध, वर्गीकरण, पॉवर-अप फंक्शन्स आणि सूचीबद्ध मानकांशी सुसंगत ऑपरेटिंग वर्तमान स्तर प्रदान करतात.

मायक्रोचिप PoE PD ऍप्लिकेशन्ससाठी पूरक उत्पादन देते, PD70224 आयडियल डायोड ब्रिज, जो इनपुट ध्रुवीयतेच्या संरक्षणासाठी ड्युअल डायोड ब्रिजला कमी-तोट्याचा पर्याय आहे.

मायक्रोचिप संपूर्ण संदर्भ डिझाइन पॅकेजेस आणि मूल्यांकन बोर्ड (EVBs) ऑफर करते. या डिझाइन पॅकेजेस, डिव्हाइस डेटा शीट्स किंवा ऍप्लिकेशन नोट्समध्ये प्रवेश करण्यासाठी, कृपया तुमच्या स्थानिक मायक्रोचिप क्लायंट एंगेजमेंट मॅनेजरचा सल्ला घ्या किंवा आमच्या भेट द्या webयेथे साइट www.microchip.com/poe.

तांत्रिक समर्थनासाठी, तुमच्या स्थानिक एम्बेडेड सोल्युशन्स अभियंत्यांचा सल्ला घ्या किंवा येथे जा microchipsupport.force.com/s/.

मायक्रोचिप PoE फ्रंट-एंड पीडी कंट्रोलर मुख्य वैशिष्ट्ये

खालील सर्व मायक्रोचिप PoE ची सामान्य वैशिष्ट्ये आहेत

- पीडी नियंत्रक.

- पीडी शोध स्वाक्षरी

- प्रोग्राम करण्यायोग्य पीडी वर्गीकरण स्वाक्षरी

- एकात्मिक अलगाव स्विच

- वीज बचतीसाठी, पॉवर चालू असताना 24.9 k डिटेक्शन सिग्नेचर रेझिस्टर डिस्कनेक्शन

- इनरश वर्तमान मर्यादा (सॉफ्ट स्टार्ट)

- डीसी-डीसी कन्व्हर्टरसाठी एकात्मिक 10.5V स्टार्ट-अप सप्लाय आउटपुट

- ओव्हरलोड संरक्षण

- डीसी-डीसी बल्क कॅपेसिटरसाठी अंतर्गत डिस्चार्ज सर्किटरी

- विस्तृत तापमान ऑपरेटिंग श्रेणी 40 °C ते 85 °C

- ऑन-चिप थर्मल संरक्षण

खालील तक्त्यामध्ये PoE PD कंट्रोलर्समध्ये वेगवेगळी वैशिष्ट्ये आहेत.

तक्ता 2. मायक्रोचिप PoE फ्रंट-एंड PD कंट्रोलर प्रमुख वैशिष्ट्ये

| भाग क्रमांक | आयसी प्रकार | मानके | कमाल पॉवर (प) |

कमाल वर्तमान (A) |

कमाल प्रतिकार (Ω) |

ध्वज १ | WA प्राधान्य पिन 2 |

व्हॉक्स |

| PD70100 | फ्रंट एंड | आयईईई 802.3 एएफ | 15.4 | 0.45 | 0.6 | PGOOD | नाही | होय |

| PD70200 | फ्रंट एंड | आयईईई 802.3 एएफ IEEE 802.3at |

47 | 1.123 | 0.6 | PGOOD वर 2-इव्हेंट |

नाही | होय |

| PD70210A/AL | फ्रंट एंड | आयईईई 802.3 एएफ IEEE 802.3at PoH UPoE |

95 | 2 | 0.3 | AT 4P_AT HD 4P_HD २/३ कार्यक्रम |

होय | होय |

| PD70210 | फ्रंट एंड | आयईईई 802.3 एएफ IEEE 802.3at PoH UPoE |

95 | 2 | 0.3 | AT 4P_AT HD 4P_HD PGOOD २/३ कार्यक्रम |

नाही | होय |

| PD70224 | आदर्श डायोड ब्रिज |

आयईईई 802.3 एएफ IEEE 802.3at PoH UPoE |

95 | 2 | 0.76 | N/A | N/A | N/A |

- तपशीलवार वर्णनासाठी, 4. सामान्य ऑपरेशन सिद्धांत पहा.

a AT—AT ध्वज

b 4P_AT—4-जोडी AT ध्वज

c HD—HDBaseT ध्वज

d 4P_HD—4-जोडी HDBaseT

e PGOOD - पॉवर चांगला ध्वज - WA प्रायोरिटी पिन वॉल अॅडॉप्टर कार्यक्षमतेचे समर्थन नियंत्रित करते आणि बाह्य DC स्त्रोताकडून लोडला वीज पुरवण्यासाठी सहायक पुरवठा प्राधान्य लागू करते.

PoE ओव्हरview

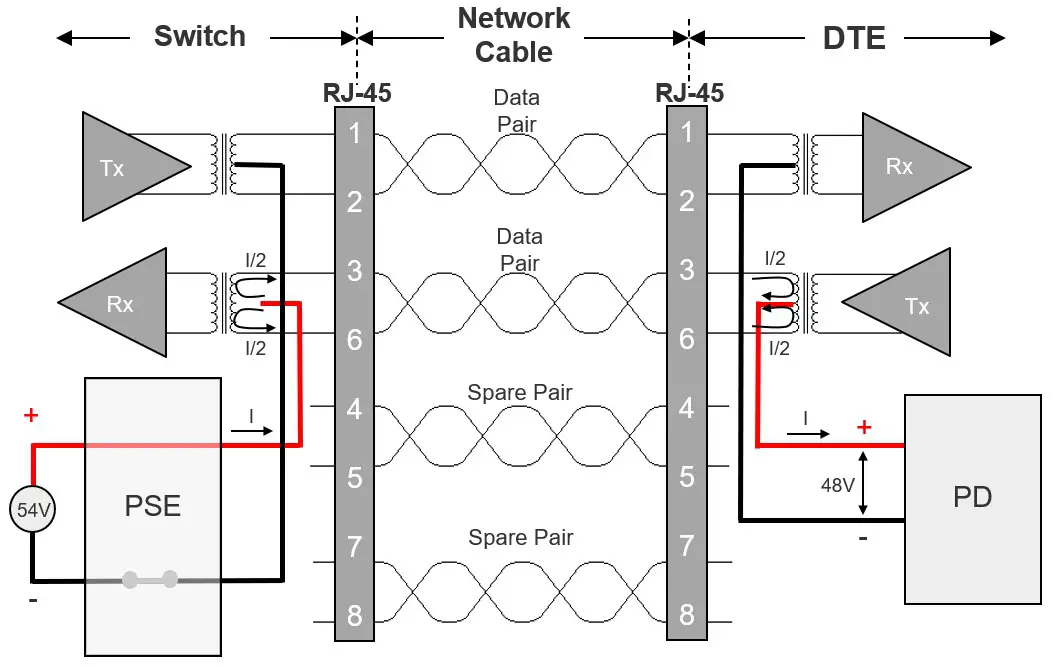

PoE मध्ये पॉवर सोर्स इक्विपमेंट (PSE), इथरनेट किंवा नेटवर्क केबल (सामान्यत: इन्फ्रास्ट्रक्चरमध्ये असते) जास्तीत जास्त 100 मीटर लांबी आणि पॉवर्ड डिव्हाईस (PD) यांचा समावेश असतो जो डेटा आणि पॉवर दोन्ही स्वीकारतो. इथरनेट केबलचा पॉवर इंटरफेस (PI). PI हा साधारणपणे आठ पिन RJ45 प्रकारचा कनेक्टर असतो. PSE सामान्यत: इथरनेट स्विच किंवा मिडस्पॅनमध्ये राहतो. PD ज्याला कधीकधी डेटा टर्मिनल इक्विपमेंट (DTE) म्हणून संबोधले जाते त्यामध्ये राहतो. खालील आकडे या मांडणीचे आकृत्या दाखवतात.

आकृती 1-1. डेटावर टू-पेअर पॉवर – पर्यायी A

आकृती 1-2. दोन-जोडी पॉवर ओव्हर स्पेअर-पर्यायी बी

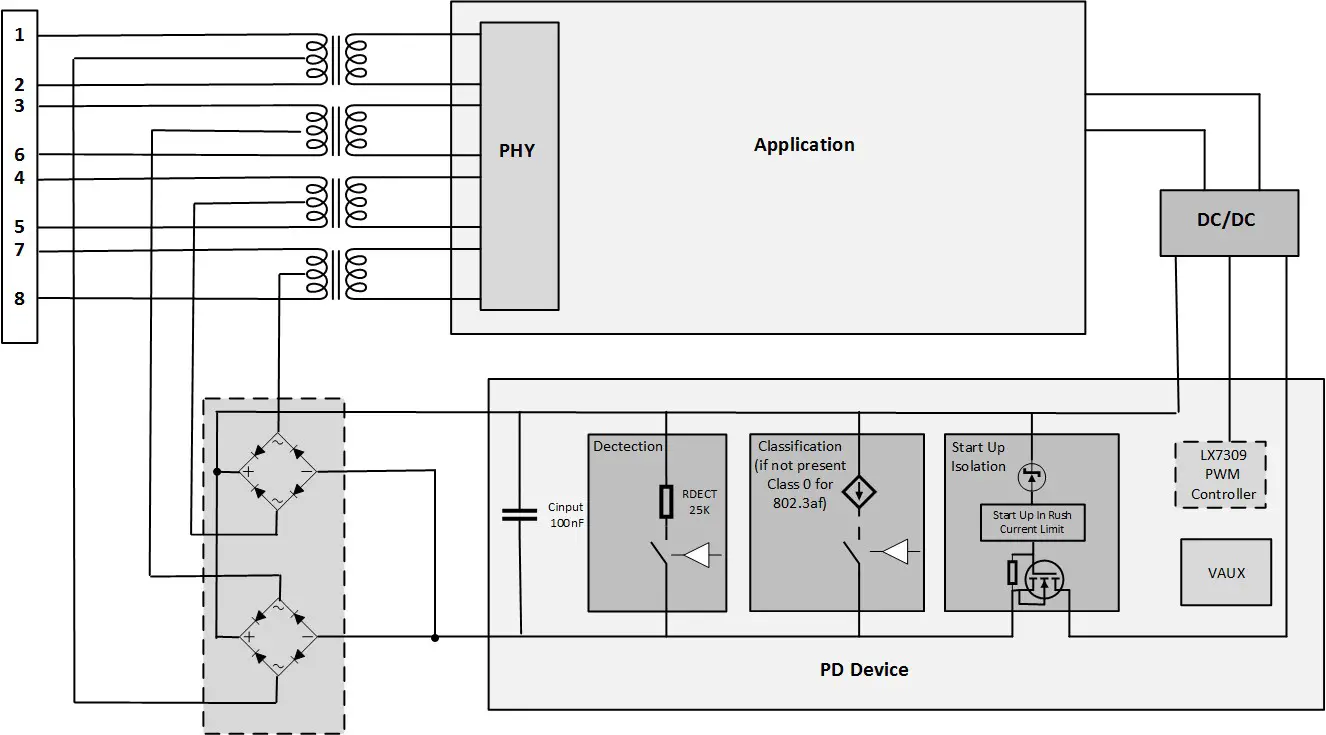

आकृती 1-3. बेसिक पीडी ब्लॉक डायग्राम

पीडी खालील कार्ये प्रदान करते.

- पोलॅरिटी प्रोटेक्शन-वॉल्यूमtagPI वर ध्रुवीयतेची मानकांद्वारे हमी दिलेली नाही. म्हणून, PD इनपुटवर योग्य ध्रुवता सुनिश्चित करण्यासाठी डायोड ब्रिज वापरला जातो. ऑप्टिमाइझ पॉवर लॉस आणि पीसीबी क्षेत्रासाठी, मायक्रोचिप PD70224 आयडियल डायोड ब्रिज वापरा. मानक डायोड ब्रिज देखील वापरले जाऊ शकतात.

- डिटेक्शन - शोधण्यासाठी स्वाक्षरी प्रदान करते.

- वर्गीकरण-वर्गीकरण स्वाक्षरीसाठी स्वाक्षरी प्रदान करते.

- स्टार्ट-अप - शोध आणि वर्गीकरणानंतर, एक नियंत्रित उर्जा अनुप्रयोग प्रदान करते.

- अलगाव- PoE डोमेनमध्ये पृथ्वीच्या जमिनीपासून आणि वापरकर्त्याच्या प्रवेशयोग्य भागांपासून 1500 VAC अलगाव असणे आवश्यक आहे. वेगळ्या DC/DC कनव्हर्टरद्वारे हे अलगाव प्रदान करण्याची शिफारस केली जाते. नॉन-आयसोलेटेड डिझाईन्ससह, शेवटच्या ऍप्लिकेशनला हे अलगाव प्रदान करावे लागेल. असा एक समज आहे की नॉन-आयसोलेटेड डिझाइनमुळे खर्चाची बचत होते, परंतु प्रत्यक्षात हे खरे नाही कारण तुम्हाला सुरुवातीच्या स्टार्ट-अप नंतर कंट्रोलरचा पूर्वाग्रह प्रदान करणे आवश्यक आहे, याचा अर्थ सहायक बूटस्ट्रॅप वाइंडिंगसह कस्टम इंडक्टर.

- DC/DC स्टार्ट-अपसाठी VAUX-बायस. सर्व Microchip PoE PD IC चे नियमन केलेले व्हॉल्यूम उपलब्ध आहेtage आउटपुट, VAUX, बाह्य DC/DC नियंत्रकासाठी स्टार्ट-अप पुरवठा म्हणून वापरला जाईल. VAUX हे कमी करंट, कमी ड्युटी सायकल आउटपुट आहे, जोपर्यंत बाह्य बूटस्ट्रॅप पुरवठा घेत नाही तोपर्यंत क्षणोक्षणी विद्युत प्रवाह प्रदान करते.

- PWM कंट्रोलर आणि DC/DC – उच्च PoE व्हॉल्यूममध्ये रूपांतरित करतेtage खाली नियमन पुरवठा खंडtage अनुप्रयोगाद्वारे वापरले जाते. PWM एक बाह्य मायक्रोचिप उपकरण असू शकते किंवा मायक्रोचिप PD पॅकेजमध्ये एकत्रित केले जाऊ शकते.

खालील तक्त्या PSE आणि PD साठी PoE मानकांची तुलना करतात. HDBaseT (PoH) मानक IEEE 802.3at टाइप 2 केबल प्रकारांचे अनुसरण करते. तथापि, त्याच्या उच्च समर्थित करंटमुळे, ते एका केबल बंडलमधील केबल्सची संख्या मर्यादित करते.

तक्ता 1-1. PSE साठी IEEE 802.3af, 802.3at, आणि HDBaseT मानके

| PSE आवश्यकता | IEEE® 802.3af किंवा IEEE 802.3 टाइप 1 वर | IEEE 802.3at टाइप 2 | 2-जोडी HDBaseT प्रकार 3 | 4-जोडी HDBaseT प्रकार 3 |

| येथे हमी शक्ती PSE आउटपुट |

15.4W | 30W | 47.5W | 95W |

| PSE आउटपुट व्हॉल्यूमtage | 44V ते 57V | 50V ते 57V | 50V ते 57V | 50V ते 57V |

| येथे हमी वर्तमान | अप सह 350 mA DC | अप सह 600 mA DC | अप सह 950 mA DC | 2x 950 mA DC सह |

| PSE आउटपुट | 400 mA पर्यंत | 686 mA पर्यंत | 1000 mA पर्यंत | 2000 mA पर्यंत शिखर |

| कमाल केबल लूप प्रतिकार | 200 | 12.50 | 12.50 | 12.50 |

| भौतिक स्तर वर्गीकरण | ऐच्छिक | अनिवार्य | अनिवार्य | अनिवार्य |

| समर्थित भौतिक स्तर वर्गीकरण वर्ग | इयत्ता 0 ते 4 | वर्ग 4 अनिवार्य | वर्ग 4 अनिवार्य | वर्ग 4 अनिवार्य |

| डेटा लिंक वर्गीकरण | ऐच्छिक | ऐच्छिक | ऐच्छिक | ऐच्छिक |

| 2-घटना वर्गीकरण | आवश्यक नाही | अनिवार्य | आवश्यक नाही | आवश्यक नाही |

| 3-घटना वर्गीकरण | आवश्यक नाही | आवश्यक नाही | अनिवार्य | अनिवार्य |

| 4-जोडी पॉवर फीडिंग | परवानगी नाही | परवानगी दिली | NA | परवानगी दिली |

| संवाद | 10/100 बेसT | 10/100/1000 बेसT | 10/100/1000/ | 10/100/1000/ |

| संवाद समर्थित |

10/100 बेसT (मध्यभागी) 10/100/1000 बेसT (स्विच) |

10/100/1000 बेसT मिडस्पॅन्ससह (दोन्ही प्रकार 1 आणि प्रकार 2) |

10/100/1000/ 10000 बेसT |

10/100/1000/ 10000 बेसT |

तक्ता 1-2. PD साठी IEEE 802.3af, 802.3at आणि HDBaseT मानके

| पीडी आवश्यकता | IEEE 802.3af किंवा IEEE 802.3at प्रकार 1 |

IEEE 802.3at टाइप 2 | HDBaseT प्रकार 3 |

| 100 मीटर केबल नंतर पीडी इनपुटवर हमी दिलेली उर्जा | 12.95W | 25.50W | 72.40W |

| पीडी इनपुट व्हॉल्यूमtage | 37V ते 57V | 42.5V ते 57V | 38.125V ते 57V |

| पीडी इनपुटवर कमाल डीसी करंट | 350 mA | 600 mA | 1.7A |

| भौतिक स्तर वर्गीकरण | अनिवार्य (वर्ग नाही = वर्ग 0) |

अनिवार्य | अनिवार्य |

| समर्थित भौतिक स्तर वर्गीकरण वर्ग | इयत्ता 0 ते 4 | वर्ग 4 अनिवार्य | वर्ग 4 अनिवार्य |

| डेटा लिंक वर्गीकरण | ऐच्छिक | ऐच्छिक | ऐच्छिक |

| 2-घटना वर्गीकरण | आवश्यक नाही | अनिवार्य | ऐच्छिक |

| 4-जोडी पॉवर प्राप्त करणे | परवानगी दिली | परवानगी दिली | सपोर्ट करतो |

| संप्रेषण समर्थित | 10/100 बेसT (मध्यभागी) 10/100/1000 बेसT (स्विच) |

मिडस्पॅनसह 10/100/1000 बेसटी (दोन्ही प्रकार 1 आणि प्रकार 2) | 10/100/1000/10000 बेसT |

डीसी व्हॉलtage थ्रू वायर जोड्या एकतर ध्रुवीय असू शकतात. PI वर उपलब्ध PoE पॉवरच्या सर्व संभाव्य संयोजनांना सामावून घेण्यासाठी, PD70224 Ideal Diode Bridge किंवा PD बाजूला ड्युअल डायोड ब्रिजचा वापर करणे आवश्यक आहे.

डिटेक्शन टप्प्यात, मानके मानक कंप्लायंट पीडीशी केबल जोडलेली आहे की नाही हे निर्धारित करण्याच्या पद्धती परिभाषित करतात, जे पॉवर प्राप्त करण्यास सक्षम असलेले उपकरण आहे, पॉवर प्राप्त न करण्याच्या क्षमतेच्या उपकरणाशी कनेक्ट केलेले आहे किंवा डिस्कनेक्ट केलेले आहे.

ही मानके पुढील पॉवर आवश्यकता निर्धारित करण्याच्या पद्धती किंवा कनेक्ट केलेले PoE-अनुरूप PD किती पॉवर प्राप्त करण्यास सक्षम आहे आणि PD द्वारे समर्थित असलेल्या पॉवर लेव्हलचे निर्धारण करण्यासाठीच्या पद्धती परिभाषित करतात. याला वर्गीकरण टप्पा म्हणतात.

एक अनुपालन PSE PI वर ऑपरेटिंग पॉवर लागू करत नाही जोपर्यंत तो यशस्वीरित्या PoE अनुरूप PD शोधत नाही. शोध टप्प्यात, PSE कमी व्हॉल्यूमची मालिका लागू करतेtage 2.80V आणि 10.0V मधील डाळींची चाचणी करा. या डाळींच्या प्रतिसादात, PoE-अनुरूप PD ने वैध स्वाक्षरी प्रदान करणे आवश्यक आहे, ज्यासाठी 23.7 k आणि 26.3 k दरम्यान विभेदक प्रतिकार आणि 50 nF आणि 120 nF दरम्यान इनपुट कॅपेसिटन्स आवश्यक आहे. वैध शोध प्रतिरोध प्रदान करण्यासाठी, सर्व मायक्रोचिप PoE PD नियंत्रकांना बाह्य 24.9 k रेझिस्टर आवश्यक आहे. हे रेझिस्टर PD उपकरणाच्या VPP आणि RDET पिन दरम्यान जोडलेले आहे. जेव्हा मायक्रोचिप पीडी कंट्रोलर इनपुट व्हॉल्यूमचे निरीक्षण करतोtage डिटेक्शन रेंज 2.7V ते 10.1V मध्ये, ते या रेझिस्टरला PI ला आंतरिकरित्या जोडते. डिटेक्शन टप्पा संपल्यानंतर, अतिरिक्त पॉवर लॉस टाळण्यासाठी मायक्रोचिप कंट्रोलर डिटेक्शन रेझिस्टर आपोआप डिस्कनेक्ट करतो. वैध डिटेक्शन कॅपॅसिटन्स (शिफारस केलेले मूल्य 100 nF ते 82 nF) प्रदान करण्यासाठी PD डिव्हाइसच्या पिनमध्ये 100V सिरॅमिक कॅपेसिटर VPP आणि VPN दरम्यान कनेक्ट केलेले असणे आवश्यक आहे.

वैध स्वाक्षरी आढळल्यानंतर, PSE वर्गीकरण टप्पा सुरू करू शकते. 802.3af आणि 802.3at प्रकार 1 PSEs आणि PDs साठी वर्गीकरण पर्यायी आहे; आणि 802.3at प्रकार 2 आणि PoH साठी अनिवार्य आहे. PSE व्हॉल्यूम वाढवतेtage एक खंड मध्येtagनिर्दिष्ट कालावधीसाठी 15.5V ते 20.5V ची श्रेणी. याला वर्गीकरण बोट म्हणतात. एकापेक्षा जास्त बोटांची आवश्यकता असल्यास, वर्गीकरणाची बोटे मार्क व्हॉल म्हणून ओळखल्या जाणार्या बोटांनी विभक्त केली जातात.tage, जेथे PSE व्हॉल्यूम कमी करतेtage 6.3V ते 10.1V दरम्यानच्या श्रेणीत, पुन्हा विनिर्दिष्ट कालावधीसाठी.

वर्गीकरण करताना खंडtage किंवा क्लास फिंगर लावले जाते, नंतर PD ने त्याचा वर्ग सिग्नल करण्यासाठी एक स्थिर प्रवाह काढला पाहिजे. मायक्रोचिप कंट्रोलर्समध्ये वर्गीकरण स्वाक्षरी पीडी उपकरणे आरसीएलएस आणि व्हीपीएन दरम्यान पिनमध्ये जोडलेल्या रेझिस्टर आरसीएलएसद्वारे प्रोग्राम केली जाते. जेव्हा इनपुट व्हॉल्यूमtage वर्गीकरण श्रेणीमध्ये आहे, पीडी RCLS द्वारे प्रोग्रॅम केलेले वर्तमान काढते.

IEEE 802.3at प्रकार 2 अनुरूप PD 2-इव्हेंट वर्गीकरण ओळखण्यासाठी आणि अंतर्गत सर्किट्सना AT फ्लॅग सिग्नल प्रदान करण्यासाठी आवश्यक आहे जे PD AT प्रकार 2 अनुरूप PSE शी जोडलेले आहे.

3-इव्हेंट वर्गीकरण ओळखण्यासाठी आणि अंतर्गत सर्किट्सना HDBaseT ध्वज सिग्नल प्रदान करण्यासाठी PoH प्रकार 3 अनुरूप PD आवश्यक आहे जे सूचित करते की PD HDBaseT प्रकार 3 अनुरूप PSE शी जोडलेला आहे.

जर पोर्ट व्हॉल्यूमtage उपस्थित PI ड्रॉप 2.8V पेक्षा कमी आहे, PSE वर्ग माहिती रीसेट होते आणि PD ने वर्ग अवलंबित ध्वज रीसेट करणे आवश्यक आहे.

Microchip PoE PDs मध्ये एक अलग करणारा स्विच असतो जो PD ची रिटर्न साइड डिटेक्शन आणि क्लासिफिकेशन फेज दरम्यान किंवा पॉवर लॉस आणि ओव्हरलोड दरम्यान PI पासून डिस्कनेक्ट करतो. पीडी PI व्हॉल्यूमवर अलग करणारे स्विच चालू करतेtage 42V किंवा त्याहून अधिक पातळी आणि PI vol वर अलग करणारे स्विच बंद कराtage पातळी 30.5V खाली. ते स्टार्ट-अप दरम्यान सक्रियपणे 350 एमए किंवा त्यापेक्षा कमी प्रवाह मर्यादित करतात.

खालील आकडे अनुक्रमे टाइप 1 IEEE 802.3af आणि टाइप 2 IEEE 802.3at साठी मूलभूत PoE शोध, वर्गीकरण आणि पॉवर-अप क्रम दर्शवितात. वर्ग स्तर, त्यांचे संबंधित प्रवाह आणि शिफारस केलेले RCLS प्रतिरोधक टेबल 1-3 मध्ये सूचीबद्ध आहेत.

आकृती 1-4. IEEE 802.3af मानकांसाठी मूलभूत PoE शोध, वर्गीकरण आणि पॉवर-अप अनुक्रम

आकृती 1-5. 802.3 मानकांसाठी मूलभूत PoE शोध, वर्गीकरण आणि पॉवर-अप अनुक्रम

तक्ता 1-3. वर्गीकरण वर्तमान व्याख्या आणि आवश्यक वर्ग सेटिंग प्रतिरोधक

| वर्ग | वर्गीकरण दरम्यान पीडी वर्तमान ड्रॉ | RCLASS प्रतिकार मूल्ये, Ω | ||

| मि | नाममात्र | कमाल | ||

| 0 | 0 mA | NA | 4 mA | स्थापित नाही |

| 1 | 9 mA | 10.5 mA | 12 mA | 133 |

| 2 | 17 mA | 18.5 mA | 20 mA | 69.8 |

| 3 | 26 mA | 28 mA | 30 mA | 45.3 |

| 4 | 36 mA | 40 mA | 44 mA | 30.9 |

टीप: पीडी इनपुट व्हॉल्यूमtage वर्गीकरण टप्प्यात 14.5V ते 20.5V आहे.

PD702x0 आणि PD701x0 ICs वापरणे

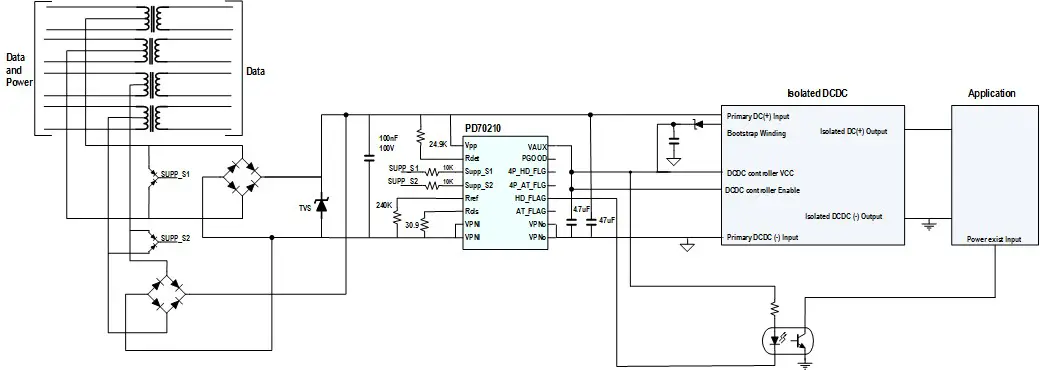

खालील चित्रात दाखवल्याप्रमाणे PD702x0 आणि PD701x0 ICs 2-जोडी आणि 4-जोडी अशा दोन्ही प्रणालींसाठी वापरले जाऊ शकतात. दोन डायोड ब्रिजमधून आउटपुट VPP (पॉझिटिव्ह बस) आणि VPNIN (नकारात्मक बस) शी जोडलेले आहेत. DC/DC कनवर्टर/अॅप्लिकेशनला आउटपुट कनेक्शन VPP आणि VPNOUT दरम्यान केले जातात. आकृती 2-1. एकल PD2/A/AL IC सह ठराविक 4- किंवा 70210-जोडी कॉन्फिगरेशन

मूलभूत इनपुट/आउटपुट कनेक्शन व्यतिरिक्त, विशिष्ट अनुप्रयोगासाठी खालील बाह्य घटक आवश्यक आहेत:

- डिटेक्शन रेझिस्टर: VPP आणि RDET पिन दरम्यान 24.9 k ±1% रेझिस्टर कनेक्ट करा. हे रेझिस्टर डिटेक्शन सिग्नेचर देण्यासाठी वापरले जाते. कमी वॅटtagई प्रकार वापरला जाऊ शकतो कारण डिटेक्शन फेज सक्रिय असताना या रेझिस्टरवर 7 mW पेक्षा कमी ताण असतो आणि पॉवर चालू झाल्यानंतर रेझिस्टर डिस्कनेक्ट होतो.

- संदर्भ प्रतिरोधक: अंतर्गत सर्किटरीसाठी रेझिस्टर सेटिंग बायस करंट आरआरईएफ पिन आणि व्हीपीएनआयएन दरम्यान कनेक्ट करणे आवश्यक आहे. PD60.4/A/AL ICs साठी 1 k ±70210% रेझिस्टर आणि PD240/PD1 साठी 70100 k ±70200% कनेक्ट करा. हा रेझिस्टर आयसीच्या जवळ स्थित असावा. कमी वॅटtagई प्रकार वापरला जाऊ शकतो (ऊर्जा अपव्यय 1 मेगावॅटपेक्षा कमी आहे).

- वर्गीकरण वर्तमान प्रतिरोधक: RCLASS पिन आणि VPNIN दरम्यान जोडलेल्या रेझिस्टरचे मूल्य वर्गीकरण टप्प्यात PD वर्तमान ड्रॉ निर्धारित करते. IEEE अनुरूप वर्गीकरण पातळीशी संबंधित मूल्ये मागील तक्त्यामध्ये प्रदान केली आहेत.

- इनपुट कॅपेसिटर: वैध ओळख स्वाक्षरीसाठी IEEE ला VPP आणि VPNIN दरम्यान 50 nF आणि 120 nF मधील कॅपेसिटन्स असणे आवश्यक आहे. सर्वोत्तम कामगिरीसाठी आणि तीक्ष्ण व्हॉल्यूमपासून चिपचे संरक्षण करण्यासाठीtagई क्षणिक, मायक्रोचिप सिरेमिक कॅपेसिटर 82 nF ते 100 nF प्रति 100V वापरण्याची शिफारस करते. ते चिपच्या व्यावहारिक तितके जवळ स्थित असले पाहिजे.

- इनपुट TVS: जर डायोड ब्रिजचा वापर केला असेल तर, मूलभूत पातळीच्या विरुद्ध मूलभूत संरक्षणासाठी व्हॉल्यूमtage ट्रान्झिएंट्स (<1 kV), दोन्ही 10×700 µS किंवा 1.2×50 µS, 58V TVS (जसे की SMBJ58A किंवा समतुल्य) VPP पिन आणि VPNIN दरम्यान कनेक्ट केलेले असणे आवश्यक आहे. सक्रिय ब्रिज PD70224 वापरला असल्यास किंवा IEC/EN 61000-4-5 (2014 Ed.3), ITU-T K21, आणि GR-1089 च्या वाढीची आवश्यकता पूर्ण करण्यासाठी वापरला असल्यास, नंतर पहा मायक्रोचिप ऍप्लिकेशन नोट AN3410.

- SUPP_S1 आणि SUPP_S2 इनपुट (केवळ PD70210/A/AL): 10 k रेझिस्टर प्रत्येक इनपुट पिन SUPP_S1 आणि SUPP_S2 शी जोडलेले असले पाहिजेत. या पिनसाठीचे सिग्नल अॅक्टिव्ह ब्रिज PD70224 च्या संबंधित पिनमधून किंवा मागील आकृतीमध्ये दाखवल्याप्रमाणे नियमित डायोड ब्रिज वापरल्यास सहायक रेक्टिफायरकडून येतात. PD70210/A/AL मधील हे इनपुट काही लेगेसी 4-जोडी मिडस्पॅनसह AT आणि 4-जोडी AT ध्वज सेट करण्यास अनुमती देतात जे प्रत्येक जोडी सेटवर फक्त एक वर्गीकरण पल्स प्रदान करतात. SUPP_S1 आणि SUPP_S2 पिन उघडे राहिल्यास, PD70210/A/AL मधील ध्वजांची स्थिती खालील सारणीनुसार आहे.

तक्ता 2-1. SUPP_S70210 आणि SUPP_S1 पिन जोडलेले नसताना PD2/A/AL ध्वजांची स्थिती

| बोटांची संख्या (N-इव्हेंट वर्गीकरण) |

AT ध्वज | HDBaseT ध्वज | 4-जोडी AT ध्वज | 4-पेअर HDBaseT ध्वज |

| 1 | हाय झेड | हाय झेड | हाय झेड | हाय झेड |

| 2 | 0 व्ही | हाय झेड | हाय झेड | हाय झेड |

| 3 | 0 व्ही | 0 व्ही | हाय झेड | हाय झेड |

| 4 | 0 व्ही | 0 व्ही | 0 व्ही | हाय झेड |

| 5 | 0 व्ही | 0 व्ही | 0 व्ही | हाय झेड |

| 6 | 0 व्ही | 0 व्ही | 0 व्ही | 0 व्ही |

- पॉवर गुड (फक्त PD70100, PD70200, आणि PD70210): PGOOD पिनवर ओपन ड्रेन पॉवर गुड सिग्नल उपलब्ध आहे. स्टार्ट-अप नंतर, PGOOD ध्वज कमी व्हॉल्यूम तयार करतोtagई VPNOUT च्या संदर्भात पॉवर रेल तयार असल्याची माहिती ऍप्लिकेशनला द्या. पुल-अप व्हॉलtage या पिनवर PD20 साठी 70210V आणि VPP व्हॉल्यूम पर्यंत मर्यादित आहेtage PD7010x/PD7020x साठी. DC-DC च्या बूटस्ट्रॅप वाइंडिंग आउटपुटद्वारे पॉवर गुड देखील खेचला जाऊ शकतो, अशा स्थितीत, स्टार्टअप दरम्यान VAUX मधून अतिरिक्त विद्युत प्रवाह टाळण्यासाठी ते VAUX वरून Schottky डायोडद्वारे वेगळे केले जाणे आवश्यक आहे.

टीप: PGOOD चा वापर बाह्य ऍप्लिकेशन स्टार्ट-अप करण्यासाठी केला असल्यास, ऍप्लिकेशनने IEEE 80 द्वारे आवश्यक ऑपरेटिंग स्टेट विलंबासाठी 802.3 ms inrush प्रदान करणे आवश्यक आहे. - PSE प्रकार अहवाल देणारे ध्वज: हे ध्वज s असू शकतातampजास्तीत जास्त वीज वापरण्यावर निर्णय घेण्यासाठी अर्जाच्या नेतृत्वाखाली. हे सर्व झेंडे ओपन ड्रेन पिन आहेत. पुल-अप व्हॉलtage या सर्व पिनवर PD20/A/AL साठी 70210V आणि VPP व्हॉल्यूमपर्यंत मर्यादित आहेtage PD70200/PD70100 साठी. DC-DC च्या बूटस्ट्रॅप वाइंडिंग आउटपुटद्वारे ध्वजांना वर खेचले जाऊ शकते, अशा परिस्थितीत, ते VAUX मधील Schottky डायोडद्वारे वेगळे केले जाणे आवश्यक आहे. फ्लॅग स्टेट पोर्ट स्टार्टअपवर फक्त एकदाच सेट केले जाते आणि ऑपरेटिंग स्टेट विलंब संपला आहे असे ऍप्लिकेशन सूचित करण्यासाठी किमान 80 ms विलंबाने दावा केला जातो. पोर्ट चालू केल्यानंतर SUPP_S1 आणि SUPP_S2 पिन बदलत असल्यास, त्यानुसार ध्वज बदलत नाहीत.

- AT_FLAG (PD70210/A/AL आणि PD70200 वर उपलब्ध): जेव्हा प्रकार 2 PSE आणि PD एकमेकांना वर्गीकरणाद्वारे एकमेकांना ओळखतात तेव्हा हा ध्वज सक्रिय होतो.

- HD_FLAG (PD70210/A/AL वर उपलब्ध): जेव्हा HDBaseT PSE आणि PD एकमेकांना वर्गीकरणाद्वारे एकमेकांना ओळखतात तेव्हा हा ध्वज सक्रिय होतो.

- 4P_AT_FLAG (PD70210/A/AL वर उपलब्ध): जेव्हा PSE आणि PD ची 4-जोडी आवृत्ती वर्गीकरणाद्वारे एकमेकांना ओळखतात तेव्हा हा ध्वज सक्रिय होतो.

- 4P_HD_FLAG (PD70210/A/AL वर उपलब्ध): 4-जोडी (ट्विन) HDBaseT PSE तेव्हा हा ध्वज सक्रिय कमी होतो

आणि पीडी वर्गीकरणाद्वारे एकमेकांना ओळखतात.

- VAUX आउटपुट: VAUX हे बाह्य DC-DC कनवर्टर कंट्रोलरसाठी स्टार्ट-अप पुरवठा म्हणून वापरण्यासाठी उपलब्ध असलेले कमी पॉवरचे नियमन केलेले आउटपुट आहे. स्टार्ट-अप केल्यानंतर, DC-DC कनवर्टरच्या सहाय्यक (बूटस्ट्रॅप्ड) विंडिंगमधून VAUX समर्थित असणे आवश्यक आहे. VAUX आउटपुटसाठी किमान 4.7 µF चे सिरेमिक कॅपेसिटर VAUX पिन आणि VPNOUT पिन यांच्यामध्ये थेट जोडले जाणे आवश्यक आहे आणि डिव्हाइसच्या जवळ भौतिकरित्या ठेवले पाहिजे.

बाह्य डीसी स्त्रोतासह ऑपरेशन

PD70210A/AL IC चा वापर करणारे PD ऍप्लिकेशन बाह्य सहाय्यक उर्जा स्त्रोत (DC वॉल अडॅप्टर) प्राधान्य कार्य प्रदान करतात. सर्वसाधारणपणे, बाह्य स्त्रोतासह शक्ती प्रदान करण्याच्या तीन पद्धती आहेत:

- बाह्य स्रोत थेट PD इनपुट (VPP ते VPNIN) शी जोडलेले आहे. यासाठी बाह्य स्रोत आउटपुट व्हॉल्यूम आवश्यक आहेtage कोणत्याही लोडवर किमान 42V आणि कमाल लोडवर 36V पेक्षा जास्त असावे. अॅडॉप्टरला OR-ing डायोडद्वारे VPP किंवा VPNIN पासून वेगळे करणे आवश्यक आहे. हे कॉन्फिगरेशन अडॅप्टरला प्राधान्य देत नाही आणि PD70210, PD70100 आणि PD70200 सह वापरले जाऊ शकते.

- बाह्य स्रोत थेट PD आउटपुटशी जोडलेले आहे (VPP आणि VPNOUT दरम्यान). बाह्य स्रोत VPP किंवा VPNOUT मधून OR-ing diode द्वारे वेगळे करणे आवश्यक आहे. अडॅप्टर प्राधान्यासाठी, फक्त PD70210A/AL वापरणे आवश्यक आहे.

- बाह्य स्रोत थेट ऍप्लिकेशनच्या निम्न व्हॉल्यूमशी जोडलेला आहेtage पुरवठा रेल (DC-DC कनवर्टरचे आउटपुट). बाह्य स्रोत हे ऍप्लिकेशन पॉवर सप्लायच्या आउटपुटमधून एकतर स्विच केलेले कनेक्शन, डायोड किंवा वेगळ्या रेग्युलेटरद्वारे वेगळे केले जाणे आवश्यक आहे जे फक्त विद्युत प्रवाह (करंट सिंक करत नाही).

खालील तीन आकडे माजी दाखवतातampबाह्य भिंत अडॅप्टरसह कॉन्फिगर केलेले PD70210A/AL चे लेस. अधिक तपशीलांसाठी आणि व्हॉल्यूमच्या शिफारस केलेल्या मूल्यांसाठीtage dividers, AN3472 पहा: PoE मध्ये सहाय्यक शक्ती लागू करणे. आकृती 3-1. PD70210 इनपुटशी जोडलेली सहाय्यक उर्जा

आकृती 3-1. PD70210 इनपुटशी जोडलेली सहाय्यक उर्जा

आकृती 3-2. PD70210A आउटपुटशी जोडलेली सहायक उर्जा

आकृती 3-3. ऍप्लिकेशन सप्लायशी जोडलेली सहाय्यक शक्ती

सामान्य ऑपरेशन सिद्धांत

इव्हेंट थ्रेशोल्ड

PD ICs व्हॉल्यूमवर अवलंबून वेगवेगळ्या राज्यांमध्ये स्विच करतातtage VPP आणि VPNIN पिन दरम्यान.

- VPPVPNIN= 1.3V ते 10.1V (वाढते व्हॉल्यूमtage): डिटेक्शन रेझिस्टर RDET VPP आणि VPNIN दरम्यान जोडलेले आहे.

- VPPVPNIN= 10.1V ते 12.8V (वाढते व्हॉल्यूमtage): डिटेक्शन रेझिस्टर RDET VPNIN वरून डिस्कनेक्ट केले आहे.

- VPPVPNIN= 11.4V ते 13.7V (वाढते व्हॉल्यूमtage): वर्गीकरण वर्तमान स्रोत VPP आणि VPNIN दरम्यान जोडलेले आहे. हा थ्रेशोल्ड RCLASS द्वारे सेट केलेला प्रोग्राम केलेला वर्तमान ड्रॉ स्थापित करतो. वर्तमान परिमाण IEEE 802.3at आणि HDBaseT मानकांनुसार वर्ग पातळी सेट करते. हे कार्य IEEE 802.3af अनुरूप PD साठी पर्यायी आहे आणि IEEE 802.3at आणि HDBaseT अनुरूप PD साठी अनिवार्य आहे. VPP वाढत्या व्हॉल्यूम दरम्यान वर्गीकरण वर्तमान स्रोत कनेक्ट केलेले राहतेtage 20.9V पर्यंत.

- VPPVPNIN= 20.9V ते 23.9V (वाढते व्हॉल्यूमtage): वर्गीकरण वर्तमान स्रोत डिस्कनेक्ट आहे. वर्गीकरण चालू स्त्रोताच्या थ्रेशोल्ड सक्षम आणि अक्षम करा दरम्यान काही हिस्टेरेसिस आहे.

- VPPVPNIN= 4.9V ते 10.1V (फॉलिंग व्हॉल्यूमtage): हा खूण खंड आहेtage श्रेणी. IC VPPVPNIN व्हॉल्यूम ओळखेलtage वर्गीकरण वर्तमान स्रोत कनेक्ट थ्रेशोल्ड पासून घसरण थ्रेशोल्ड 2 घटना वर्गीकरण स्वाक्षरी एक घटना म्हणून चिन्हांकित करण्यासाठी. लेव्हल इव्हेंट चिन्हांकित करण्यासाठी वर्गांची संख्या IC ला त्यांच्या सक्रिय निम्न स्थितीवर संबंधित ध्वज सेट करण्यास प्रवृत्त करेल.

- VPPVPNIN= 36V ते 42V (वाढते व्हॉल्यूमtage): अलगाव स्विच ऑफ स्टेटमधून इनरश करंट लिमिट (सॉफ्ट स्टार्ट) मोडवर स्विच केला जातो. या मोडमध्ये, अलगाव स्विच डीसी करंटला 240 mA (नमुनेदार) पर्यंत मर्यादित करते. सॉफ्ट स्टार्ट मोड दरम्यान वर्तमान मर्यादा सर्किटरी व्हॉल्यूमचे निरीक्षण करतेtage अलगाव स्विच (VPNOUTVPNIN) मध्ये फरक आणि इनरश करंट राखतो. इनरश चालू मर्यादा दरम्यान अंतर्गत MOSFET रेखीय मोडमध्ये कार्य करते.

जेव्हा VPNOUTVPNIN 0.7V किंवा त्याहून कमी होते, तेव्हा अलगाव स्विच इनरश करंट मर्यादा अक्षम केली जाते, VAUX सक्षम केले जाते, पृथक्करण स्विच 2.2A (जास्तीत जास्त) वर्तमान संरक्षणासह पूर्णपणे चालू केले जाते आणि फ्लॉग विलंबानंतर संबंधित ध्वज निश्चित केले जातात, जे किमान 80 आहे ms - VPPVPNIN= 30.5V ते 34.5V (फॉलिंग व्हॉल्यूमtage): पृथक्करण स्विच बंद केले आहे, VPNIN आणि VPNOUT मध्ये उच्च प्रतिबाधा स्थापित करते. बल्क कॅपेसिटर डिस्चार्ज फंक्शन सक्षम केले आहे आणि जोपर्यंत व्हॉल्यूममधील फरक आहे तोपर्यंत ते सक्षम राहतेtages VPP आणि VPNOUT 30V आणि 7V दरम्यान राहते. जर सहायक उर्जा स्त्रोत वापरला असेल, तर त्याचा व्हॉल्यूमtage एकतर 34.5V च्या वर असणे आवश्यक आहे, किंवा स्त्राव प्रवाह रोखण्यासाठी VPNOUT आणि सहायक उर्जा स्त्रोताच्या रिटर्न दरम्यान एक अलगाव डायोड जोडणे आवश्यक आहे.

- VPPVPNIN= 2.8V ते 4.85V (फॉलिंग व्हॉल्यूमtage): डिटेक्शन रेझिस्टर RDET या थ्रेशोल्डवर पुन्हा कनेक्ट केले आहे. जेव्हा VPPVPNIN vol. RDET डिस्कनेक्ट होतेtage 1.1V पेक्षा कमी होते.

Inrush वर्तमान मर्यादा

सिस्टीम स्टार्ट-अप झाल्यावर बल्क कॅपेसिटरच्या प्रारंभिक चार्ज-अप दरम्यान विद्युत प्रवाह मर्यादित करण्यासाठी इनरश करंट मर्यादा आवश्यक आहे आणि PoE मानकांनुसार आवश्यक आहे. मोठे इनरश प्रवाह मोठे व्हॉल्यूम तयार करू शकतातtage PI वर sags, ज्यामुळे इव्हेंट थ्रेशोल्डशी (जसे की AT_FLAG) जोडलेली सिस्टीम फंक्शन्स त्यांच्या सुरुवातीच्या स्थितीत रीसेट होऊ शकतात. सॉफ्ट स्टार्ट वर्तमान मर्यादा लक्षणीय प्रमाणात कमी करेलtagई स्टार्ट-अप वर खाली.

पूर्णतः डिस्चार्ज केलेल्या बल्क कॅपेसिटरमध्ये स्टार्ट-अप केल्याने मोठ्या प्रमाणात कॅपेसिटन्सच्या आकारावर अवलंबून असलेल्या कालावधीसाठी आयसोलेशन स्विचमध्ये मोठ्या प्रमाणात उर्जा नष्ट होते. कमाल प्रारंभिक व्हॉलtage ड्रॉप ओलांडून अलगाव स्विच सुमारे 42V असू शकतो. पृथक्करण स्विचद्वारे विखुरलेली कमाल उर्जा बल्क कॅपेसिटर चार्ज झाल्यामुळे कमी होते, शेवटी स्विच पूर्णपणे चालू असताना सामान्य ऑपरेटिंग पॉवर अपव्ययापर्यंत कमी होते. सॉफ्ट स्टार्ट मोडमधून सामान्य ऑपरेशन मोडवर स्विच करण्यासाठी लागणारा कालावधी खालील सूत्र वापरून मोजला जाऊ शकतो:

T = ((V 0.7) × C) / I

कुठे:

I = सॉफ्ट स्टार्ट दरम्यान IC चा प्रवाह (सामान्यत: 240 mA)

C= एकूण इनपुट बल्क कॅपेसिटन्स

V= आरंभिक VPNOUTVPNIN व्हॉल्यूमtage सॉफ्ट स्टार्टच्या सुरुवातीला (VMAX = VPP)

बल्क कॅपेसिटरचे कमाल मूल्य 240 μF आहे.

बल्क कॅपेसिटर डिस्चार्ज

PD70210/A/AL ICs ऍप्लिकेशन बल्क कॅपेसिटरचे डिस्चार्ज प्रदान करतात जेव्हा VPPVPNIN फॉलिंग व्हॉल्यूमtage पृथक्करण स्विच टर्न-ऑफ खाली थेंब. हे वैशिष्ट्य हे सुनिश्चित करते की ऍप्लिकेशन बल्क कॅपेसिटन्स डिटेक्शन रेझिस्टरद्वारे डिस्चार्ज होत नाही, ज्यामुळे डिटेक्शन सिग्नेचर अयशस्वी होऊ शकते आणि PSE ला PD सुरू करण्यापासून रोखू शकते. सक्षम असताना, डिस्चार्ज फंक्शन 22.8 mA चा किमान नियंत्रित डिस्चार्ज करंट प्रदान करते, जो VPP पिनमधून, पृथक् MOSFET च्या बॉडी डायोडद्वारे आणि VPNOUT पिनद्वारे बाहेर जातो. डिस्चार्ज सर्किटरी मॉनिटर्स व्हॉलtage VPPVPNOUT मधील फरक, आणि सक्रिय राहते तर फरक voltage 7V (VPPVPNOUT) 30V आहे. डिस्चार्ज करण्यासाठी जास्तीत जास्त वेळ मोजण्यासाठी खालील समीकरण वापरा:

T = ((V 7V) × C)/0.0228

कुठे:

C= एकूण इनपुट बल्क कॅपेसिटन्स

V= आरंभिक VPPVPNOUT खंडtage अलगाव स्विच बंद करताना

Example: प्रारंभिक कॅपेसिटर व्हॉल्यूमसाठीtag32V चा e, 240 µF कॅपेसिटरला 220V स्तरावर डिस्चार्ज होण्यासाठी 7 ms लागतात.

डिस्चार्ज ऑपरेशनमध्ये टायमर असतो आणि तो किमान 430 ms साठी सक्रिय असतो.

सहायक खंडtage-VAUX

सर्व मायक्रोचिप PD IC चे नियमन केलेले व्हॉल्यूम उपलब्ध आहेtage आउटपुट, VAUX, बाह्य DC/DC नियंत्रकासाठी स्टार्ट-अप पुरवठा म्हणून वापरला जाईल. VAUX हे कमी करंट, कमी ड्युटी सायकल आउटपुट आहे, जोपर्यंत बाह्य बूटस्ट्रॅप पुरवठा घेत नाही तोपर्यंत क्षणोक्षणी विद्युत प्रवाह प्रदान करते. स्थिर ऑपरेशनसाठी VAUX आणि पॉवर ग्राउंड पिन दरम्यान 4.7 F किंवा त्याहून अधिक कॅपेसिटर कनेक्ट करा.

VAUX आउटपुट नाममात्र 10.5V वर नियमन केले जाते आणि 10 ms साठी 10 mA चे पीक करंट पुरवते. (PD5/ PD70200 साठी 70100 एमएस). PD4x साठी सतत प्रवाह 7021 mA आणि PD2x/PD7020x साठी 7010 mA आहे. सामान्यतः, VAUX आउटपुट उच्च व्हॉल्यूमच्या बूटस्ट्रॅप्ड पुरवठ्याशी जोडलेले असतेtage (जसे की पृथक DC/DC कनवर्टर ट्रान्सफॉर्मरमधून दुरुस्त केलेले सहायक आउटपुट). VAUX आउटपुट विद्युत प्रवाह बुडत नाही. एकदा बूटस्ट्रॅप व्हॉल्यूमtage VAUX आउटपुट व्हॉल्यूम ओलांडतेtage लेव्हल, VAUX आउटपुट यापुढे वर्तमान प्रदान करणार नाही आणि DC-DC कनवर्टरच्या ऑपरेशनसाठी पारदर्शक असेल. कमीत कमी आउटपुट व्हॉल्यूमसाठी सर्व ऑपरेटिंग परिस्थितीत सुधारित बूटस्ट्रॅप्ड आउटपुट डिझाइन करण्याची शिफारस केली जाते.tag12.5V चा e.

सॉफ्ट स्टार्ट मोड दरम्यान किंवा जेव्हा पृथक्करण स्विच बंद केले जाते, तेव्हा VAUX आउटपुट VPP घसरून अक्षम केले जाते.

PGOOD आउटपुट

PD70210, PD70100, आणि PD70200 ICs एक ओपन ड्रेन आउटपुट प्रदान करतात जे पॉवर चांगली स्थिती दर्शवतात. हे आउटपुट सक्रिय कमी असल्याचे प्रतिपादन करते जेव्हा व्हॉल्यूमtage VPP आणि VPNOUT मधील अंदाजे 40V पर्यंत पोहोचते. खात्री केल्यावर, PGOOD आउटपुट 5 mA च्या वर्तमान सिंक क्षमतेसह जमिनीवर स्विच करते. जेव्हा VPPVPNIN voltage आयसोलेशन स्विच टर्न-ऑफ थ्रेशोल्डच्या खाली येते, PGOOD आउटपुट उच्च प्रतिबाधा स्थितीवर परत सेट करते.

हे आउटपुट शोधण्यासाठी वापरले जाऊ शकते जेव्हा PI व्हॉल्यूमtage ऑपरेटिंग रेंजमध्ये आहे.

PD70210A/AL मध्ये PGOOD आउटपुट नाही. अशी कार्यक्षमता आवश्यक असल्यास, VAUX आउटपुट एक पर्याय म्हणून वापरला जाऊ शकतो. जर तुम्ही बाह्य लहान सिग्नल N-चॅनेल FET च्या गेटला VAUX बांधला असेल आणि त्याचा स्रोत VPNOUT ला असेल, तर या FET चा ड्रेन PGOOD बदली म्हणून वापरला जाऊ शकतो.

WA_EN इनपुट (केवळ PD70210A/AL)

हा इनपुट पिन VPP आणि VPNOUT मधील बाह्य उर्जा इनपुट कनेक्शनसाठी वापरला जातो. आकृती 3-1 पहा. एक रेझिस्टर विभाजक R1 आणि R2 VPP आणि VPNOUT दरम्यान जोडलेले आहे. हे प्रतिरोधक पी-चॅनेल FET टर्न-ऑन थ्रेशोल्ड सेट करतात. 100V कमी सिग्नल P-ch FET गेट आणि स्त्रोत R1 शी कनेक्ट केलेले असणे आवश्यक आहे. P-ch ड्रेन R3 रेझिस्टरद्वारे WA_EN इनपुटशी जोडलेले आहे. R4 रेझिस्टर WA_EN आणि VPNIN दरम्यान जोडलेले आहे. R3 आणि R4 लेव्हल सेट करतात ज्यामध्ये वैध WA इनपुट आढळले आहे. WA_EN इनपुटसाठी मानक तर्क पातळी आवश्यक आहे. जेव्हा WA_EN इनपुट जास्त असते, तेव्हा PD70210A/AL अलगाव स्विच बंद केला जातो आणि सर्व ध्वज निश्चीत केले जातात-निम्न स्तरावर बदलले जातात. रेझिस्टर निवड मार्गदर्शक ऍप्लिकेशन नोट AN3472 मध्ये निर्दिष्ट केले आहे: PDs साठी सहाय्यक शक्ती.

SUPP_S1 आणि SUPP_S2 इनपुट (केवळ PD70210A/AL)

SUPP_S1 आणि SUPP_S2 इनपुट्स PD ला पॉवरचा स्त्रोत ओळखण्यास सक्षम करतात मग तो डेटा, अतिरिक्त जोड्या किंवा दोन्ही असो. यापैकी प्रत्येक इनपुटला संबंधित जोडीशी जोडण्यासाठी सामान्य कॅथोड ड्युअल डायोड आवश्यक आहे, जर पीडी उपकरणamples a उच्च पातळी 35V आणि त्यावरील या इनपुटमध्ये ते या जोडीची सक्रिय जोडी म्हणून गणना करते. विशेष PSE सोबत काम करताना हे इनपुट वापरले जातात ज्यात फक्त दोन जोड्यांवर शोध आणि वर्गीकरण असते परंतु चारही जोड्यांमध्ये शक्ती असते. SUPP_S1 आणि SUPP_S2 इनपुटमध्ये प्रत्येकाशी अनुक्रमांकात 10 k रेझिस्टर कनेक्ट केलेले असणे आवश्यक आहे. जेव्हा ही फंक्शन्स वापरली जात नाहीत, तेव्हा SUPP_S1 आणि SUPP_S2 पिन बाह्य सर्किट्समधून डिस्कनेक्ट केले जाऊ शकतात आणि VPNIN इनपुट किंवा लेफ्ट फ्लोटिंगशी कनेक्ट केले जाऊ शकतात.

PSE प्रकार फ्लॅग आउटपुट

PD702x0 आणि PD701x0 ICs उघडलेल्या ड्रेन आउटपुट प्रदान करतात जे त्याच्या शोधलेल्या वर्गीकरण पॅटर्नद्वारे PSE प्रकार दर्शवतात. आयसोलेशन स्विच सॉफ्ट स्टार्ट करंट लिमिट मोडमधून सामान्य ऑपरेशन मोडमध्ये हलवत नाही तोपर्यंत आउटपुट उच्च प्रतिबाधा स्थितीत आहे. त्यानंतर ओळखल्या गेलेल्या वर्गीकरण पद्धतीवर अवलंबून, ते कमी असल्याचे प्रतिपादन केले जाईल. प्रतिपादन केल्यावर, 5 mA च्या वर्तमान सिंक क्षमतेसह फ्लॅग्स आउटपुट जमिनीवर स्विच करते. जेव्हा VPPVPNIN voltage आयसोलेशन स्विच टर्न-ऑफ थ्रेशोल्डच्या खाली येते. ध्वज PD डिझायनरला अनुप्रयोगाशी संबंधित असलेल्या ध्वजासह कार्य करण्यास सक्षम करतात. आढळलेल्या प्रत्येक पॉवरसाठी, खालच्या पॉवरचे सर्व ध्वजही ठामपणे मांडले जातात (IE AT_FLAG AT स्तरावर आणि AT वरील सर्व पॉवर स्तरांसाठी) ठामपणे सांगितले जाते. उपलब्ध उर्जा पातळी तक्ता 2 मध्ये निर्दिष्ट केली आहे. तक्त्यामध्ये निर्दिष्ट केल्याप्रमाणे, PD वर्गीकरण बोटांच्या घटनेची गणना करते आणि त्याच्या संख्येनुसार PSE प्रकार ओळखते. SUPP_S1 आणि SUPP_S2 PD ला एक विशेष एटी लेव्हल PSE ओळखण्यास सक्षम करतात ज्याचे वर्गीकरण फक्त दोन जोड्यांवर आहे परंतु सर्व चार जोड्यांमध्ये शक्ती आहे. म्हणून, जर दोन बोटे ओळखली गेली, तर पीडी उपकरण एसamples SUPP_S1 आणि SUPP_S2 इनपुट आणि दोन्ही उच्च असल्यास, चार जोड्यांना उर्जा पुरवली जाते आणि 4P_AT ध्वज निश्चित केला जातो.

तक्ता 5-1. उपलब्ध पीडी पॉवर लेव्हल आणि फ्लॅग इंडिकेशन

| वर्ग बोटांची संख्या | SUPP_S1 | SUPP_S2 | PGOOD_ ध्वज |

AT_ ध्वज |

HD_ ध्वज |

4P_AT_ ध्वज |

4P_HD_ ध्वज |

उपलब्ध पॉवर लेव्हल |

| 1 | X | X | 0 व्ही | हाय झेड | हाय झेड | हाय झेड | हाय झेड | 802.3 AF पातळी/ 802.3 AT प्रकार 1 स्तर |

| 2 | H | L | 0 व्ही | 0 व्ही | हाय झेड | हाय झेड | हाय झेड | 802.3 AT प्रकार 2 स्तर |

| 2 | L | H | 0 व्ही | 0 व्ही | हाय झेड | हाय झेड | हाय झेड | 802.3 AT प्रकार 2 स्तर |

| 2 | H | H | 0 व्ही | 0 व्ही | हाय झेड | 0 व्ही | हाय झेड | ड्युअल 802.3 AT प्रकार 2 स्तर |

| 3 | L | H | 0 व्ही | 0 व्ही | 0 व्ही | हाय झेड | हाय झेड | HDBaseT प्रकार 3 स्तर |

| 3 | H | L | 0 व्ही | 0 व्ही | 0 व्ही | हाय झेड | हाय झेड | HDBaseT प्रकार 3 स्तर |

| 3 | H | H | 0 व्ही | 0 व्ही | 0 व्ही | 0 व्ही | हाय झेड | HDBaseT प्रकार 3 स्तर |

| 4 | X | X | 0 व्ही | 0 व्ही | 0 व्ही | 0 व्ही | हाय झेड | ड्युअल 802.3 AT प्रकार 2 स्तर |

| 5 | X | X | भविष्यासाठी राखीव | NA | ||||

| 6 | X | X | 0 व्ही | 0 व्ही | 0 व्ही | 0 व्ही | 0 व्ही | Twin HDBaseT प्रकार 3 स्तर |

थर्मल संरक्षण

PD702x0 आणि PD701x0 ICs थर्मल संरक्षण प्रदान करतात. एकात्मिक थर्मल सेन्सर अलगाव स्विच आणि वर्गीकरण वर्तमान स्रोत अंतर्गत तापमान निरीक्षण. कोणत्याही सेन्सरचा अति-तापमान थ्रेशोल्ड ओलांडल्यास, त्या सेन्सरचे संबंधित सर्किट अक्षम होईल.

त्रासमुक्त ऑपरेशन सुनिश्चित करण्यासाठी, PD IC चे उघडलेले पॅड PCB वरील तांब्याच्या क्षेत्रामध्ये बसवलेले आहे याची खात्री करणे महत्वाचे आहे जे पुरेसे उष्णता सिंक प्रदान करते.

पीसीबी लेआउट मार्गदर्शक तत्त्वे

IEEE 802.3at आणि HDBaseT मानके विशिष्ट अलगाव आवश्यकता निर्दिष्ट करतात ज्या सर्व PoE उपकरणांनी पूर्ण केल्या पाहिजेत. इनकमिंग डेटा आणि पॉवर लाईन्स आणि कोणत्याही सिग्नल, पॉवर किंवा चेसिस कनेक्शनमध्ये किमान 1500 VRMS वर अलगाव निर्दिष्ट केला आहे जो अनुप्रयोगाच्या बाहेर अंतिम वापरकर्त्याद्वारे संपर्कात येऊ शकतो. ठराविक FR4 PCB वर, 0.080 VRMS पृथक्करण आवश्यक असलेल्या लगतच्या ट्रेसमध्ये किमान 2 इंच (1500 mm) पृथक्करण अडथळा निर्माण करून ही आवश्यकता सामान्यतः पूर्ण केली जाते.

उघडलेल्या पॅडचे (VPNOUT) पुरेसे उष्मा सिंक करण्यासाठी PCB डिझाइनकडे विशेष लक्ष द्या. सर्व मायक्रोचिप पीडी आयसी पॅकेजेस पॅकेजचे थर्मल कूलिंग प्रदान करण्यासाठी एक्सपोज्ड पॅडचा वापर करतात आणि म्हणून पीसीबी डिझाइनमध्ये उघडलेल्या पॅडला जोडलेले पुरेसे तांबे क्षेत्र समाविष्ट करणे आवश्यक आहे. मल्टीलेयर बोर्डसाठी, समीप प्लेन लेयरसाठी कंडक्टिव्ह व्हिया वापरला जाऊ शकतो. लक्षात ठेवा की एक्सपोज केलेले पॅड विद्युतरित्या VPNIN शी जोडलेले आहे आणि ते VPNOUT मधून विद्युतरित्या वेगळे केले जाणे आवश्यक आहे.

प्लेन लेयर आणि एक्सपोज्ड पॅड दरम्यान थर्मल चालकता प्रदान करण्यासाठी व्हिअस वापरताना, बॅरल्स 12 मील व्यासाचे आणि (जेथे शक्य असेल तेथे) ग्रिड पॅटर्नमध्ये ठेवलेले असणे आवश्यक आहे. योग्य सोल्डर पेस्ट सोडण्यासाठी बॅरल होल प्लग किंवा टेंट केलेले असणे आवश्यक आहे. जेव्हा तंबूयुक्त छिद्रे वापरली जातात, तेव्हा सोल्डर मास्कचा समावेश करण्याचे क्षेत्र बॅरलच्या माध्यमातून 4 मिली (0.1 मिमी) मोठे असणे आवश्यक आहे.

सिंगल किंवा ड्युअल लेयर बोर्डसाठी, उघडलेल्या पॅडच्या थेट संपर्कात मोठे तांबे भरणे वापरा. 2 औंसच्या तांब्याची जाडी थर्मल कार्यक्षमता सुधारते. 2 औंस पेक्षा कमी तांब्याचे ट्रेस वापरत असल्यास, योग्य ठिकाणी ट्रेस करण्यासाठी जादा सोल्डर जोडून एकूण ट्रेस जाडी वाढविण्याची शिफारस केली जाते.

PCB डिझाइनने उच्च विद्युत् विद्युत् प्रवाहासाठी रुंद, जड तांबे ट्रेस प्रदान करणे आवश्यक आहे. 4-जोडी, विस्तारित-पॉवर PD मध्ये VPP आणि VPN टर्मिनल्ससाठी 2A चे कमाल ट्रेस प्रवाह असू शकतात. व्हीपीपी, व्हीपीएनआयएन आणि व्हीपीएनओयूटीसाठी प्रवाह वाहून नेणाऱ्या ट्रेसचा आकार कमाल करंटवर व्यावहारिकदृष्ट्या सर्वात कमी तापमान वाढ प्रदान करणे आवश्यक आहे. उदाample, किमान 15 mils रुंद 2 oz तांबे कमाल 1.6 °C तापमान वाढीसह 10A पर्यंत विद्युत् प्रवाह सामावून घेतो. जर 2 औंस पेक्षा कमी तांब्याचा ट्रेस वापरला असेल, तर किमान तापमान वाढीसह जास्तीत जास्त प्रवाह सामावून घेण्यासाठी किमान रुंदी वाढवा.

PoE सिग्नलमध्ये voltag57 VDC पर्यंत आहे. घटक कार्यरत खंडtagई विचारात घेणे आवश्यक आहे, आणि त्यानुसार घटक आकार. पृष्ठभाग माउंट प्रतिरोधक एक चांगले माजी आहेतample: 0402 रेझिस्टरमध्ये ठराविक कमाल कार्यरत व्हॉल्यूम असतोtage 50V चे स्पेसिफिकेशन्स, तर 0805 रेझिस्टर सामान्यतः 150V वर निर्दिष्ट केले जातात.

जेव्हा PD702x0 आणि PD701x0 ICs सह वापरले जाते, तेव्हा डिटेक्शन रेझिस्टर RDET फक्त PoE vol वर जोडलेले असतेtag12.8V पर्यंत आहे, आणि अन्यथा डिस्कनेक्ट केले आहे, त्यामुळे ते कमी व्हॉल्यूम असू शकतेtage प्रकार (0402).

टीप: तपशीलवार मांडणी मार्गदर्शक तत्त्वांसाठी, Microchip Application Note AN3533 पहा.

EMI विचार

चालवलेले आणि रेडिएटेड उत्सर्जन कमी करण्यासाठी आणि संभाव्य ग्राउंड लूप "ब्रेक" करण्यासाठी, EMI फिल्टर ठेवण्याची (किंवा तरतुदी सोडण्याची) शिफारस केली जाते. हा फिल्टर सामान्यत: इनपुट रेक्टिफायर ब्रिज आणि PoE PD कंट्रोलर दरम्यान ठेवला जातो आणि खालील आकृतीमध्ये दर्शविल्याप्रमाणे सामान्य मोड चोक आणि 2 kV कॉमन-मोड कॅपेसिटर समाविष्ट करतो. माजीampअशा फिल्टरची व्यावहारिक अंमलबजावणी PD7211EVB72FW-12 मूल्यांकन मंडळ वापरकर्ता मार्गदर्शक मध्ये प्रदान केली आहे. त्यात माजीample, खालील घटक फिल्टरमध्ये वापरले जातात:

- कॉमन मोड चोक पल्स पॅन P0351

- कॉमन मोड कॅपेसिटर नवशिक्या पॅन 1812B682J202NXT

आकृती 8-1. ठराविक PD70211-आधारित प्रणालीमध्ये पॉवर फ्लो

संदर्भ दस्तऐवज

सर्व मायक्रोचिप कागदपत्रे ऑनलाइन उपलब्ध आहेत www.microchip.com/poe.

- IEEE 802.3at-2015 मानक, कलम 33 (MDI द्वारे DTE पॉवर)

- HDBaseT तपशील

- PD70210/PD70210A/PD70210AL डेटा शीट

- PD70211 डेटा शीट

- PD70100/PD70200 डेटा शीट

- PD70101/PD70201 डेटा शीट

- PD70224 डेटा शीट

- PD सिस्टम सर्ज इम्युनिटी PD3410xx_PD701xx साठी AN702 डिझाइन

- AN3472 PoE मध्ये सहाय्यक शक्तीची अंमलबजावणी करणे

- AN3471 PD1x2 आणि PD802.3x3 ICs वापरून एक प्रकार 702/1 701 किंवा HDBaseT प्रकार 1 PD फ्रंट एंड डिझाइन करणे

- AN3533 PD70210(A), PD70211 सिस्टम लेआउट मार्गदर्शक तत्त्वे

पुनरावृत्ती इतिहास

| उजळणी | तारीख | वर्णन |

| B | 04/2022 | या पुनरावृत्तीमध्ये केलेल्या बदलांचा सारांश खालीलप्रमाणे आहे: • अद्ययावत सारणी 1. • अद्ययावत 7. PCB लेआउट मार्गदर्शक तत्त्वे: 0603 प्रतिरोधकांचे उल्लेख काढले. टीप जोडली. • जोडले 8. EMI विचार. • अद्यतनित 9. संदर्भ दस्तऐवज. |

| A | 06/2020 | हा या दस्तऐवजाचा प्रारंभिक मुद्दा आहे. PD1x2 आणि PD802.3x3 ICs वापरून Type702/0 701 किंवा HDBaseT Type 0 पॉवर्ड डिव्हाइस फ्रंट एंड डिझाईन करण्याचे वर्णन खालील दस्तऐवजांमध्ये केले होते: • AN209: PD1/ PD2A ICs वापरून एक प्रकार 802.3/3 70210 किंवा HDBT प्रकार 70210 PD डिझाइन करणे • AN193: PD1/PD2 वापरून एक प्रकार 802.3/70100 IEEE 70200at/af पॉवर्ड डिव्हाइस फ्रंट एंड डिझाइन करणे |

मायक्रोचिप Webसाइट

मायक्रोचिप आमच्याद्वारे ऑनलाइन समर्थन प्रदान करते webयेथे साइट www.microchip.com/. या webसाइट तयार करण्यासाठी वापरली जाते files आणि ग्राहकांना सहज उपलब्ध असलेली माहिती. उपलब्ध असलेल्या काही सामग्रीमध्ये हे समाविष्ट आहे:

- उत्पादन समर्थन – डेटा शीट आणि इरेटा, ऍप्लिकेशन नोट्स आणि एसample प्रोग्राम्स, डिझाइन संसाधने, वापरकर्त्याचे मार्गदर्शक आणि हार्डवेअर समर्थन दस्तऐवज, नवीनतम सॉफ्टवेअर प्रकाशन आणि संग्रहित सॉफ्टवेअर

- सामान्य तांत्रिक समर्थन - वारंवार विचारले जाणारे प्रश्न (FAQ), तांत्रिक समर्थन विनंत्या, ऑनलाइन चर्चा गट, मायक्रोचिप डिझाइन भागीदार कार्यक्रम सदस्य सूची

- मायक्रोचिपचा व्यवसाय - उत्पादन निवडक आणि ऑर्डरिंग मार्गदर्शक, नवीनतम मायक्रोचिप प्रेस रिलीज, सेमिनार आणि कार्यक्रमांची सूची, मायक्रोचिप विक्री कार्यालयांची सूची, वितरक आणि कारखाना प्रतिनिधी

उत्पादन बदल सूचना सेवा

मायक्रोचिपची उत्पादन बदल सूचना सेवा ग्राहकांना मायक्रोचिप उत्पादनांवर अद्ययावत ठेवण्यास मदत करते. जेव्हा जेव्हा विशिष्ट उत्पादन कुटुंबाशी संबंधित बदल, अद्यतने, पुनरावृत्ती किंवा इरेटा असेल तेव्हा सदस्यांना ईमेल सूचना प्राप्त होईल किंवा स्वारस्य असलेल्या विकास साधनाशी संबंधित.

नोंदणी करण्यासाठी, वर जा www.microchip.com/pcn आणि नोंदणी सूचनांचे अनुसरण करा.

ग्राहक समर्थन

मायक्रोचिप उत्पादनांचे वापरकर्ते अनेक माध्यमांद्वारे सहाय्य प्राप्त करू शकतात:

- वितरक किंवा प्रतिनिधी

- स्थानिक विक्री कार्यालय

- एम्बेडेड सोल्युशन्स इंजिनियर (ईएसई)

- तांत्रिक सहाय्य

समर्थनासाठी ग्राहकांनी त्यांच्या वितरक, प्रतिनिधी किंवा ESE शी संपर्क साधावा. ग्राहकांच्या मदतीसाठी स्थानिक विक्री कार्यालये देखील उपलब्ध आहेत. या दस्तऐवजात विक्री कार्यालये आणि स्थानांची सूची समाविष्ट केली आहे. च्या माध्यमातून तांत्रिक सहाय्य उपलब्ध आहे webयेथे साइट: www.microchip.com/support

मायक्रोचिप डिव्हाइसेस कोड संरक्षण वैशिष्ट्य

मायक्रोचिप उपकरणांवरील कोड संरक्षण वैशिष्ट्याचे खालील तपशील लक्षात घ्या:

- मायक्रोचिप उत्पादने त्यांच्या विशिष्ट मायक्रोचिप डेटा शीटमध्ये समाविष्ट असलेल्या तपशीलांची पूर्तता करतात.

- मायक्रोचिपचा असा विश्वास आहे की त्याचे उत्पादनांचे कुटुंब हे आज बाजारपेठेतील त्याच्या प्रकारातील सर्वात सुरक्षित कुटुंबांपैकी एक आहे, जेव्हा त्याचा वापर अपेक्षित पद्धतीने आणि सामान्य परिस्थितीत केला जातो.

- कोड संरक्षण वैशिष्ट्याचा भंग करण्यासाठी अप्रामाणिक आणि शक्यतो बेकायदेशीर पद्धती वापरल्या जातात. या सर्व पद्धती, आमच्या माहितीनुसार, मायक्रोचिप उत्पादनांचा वापर मायक्रोचिपच्या डेटा शीटमध्ये असलेल्या ऑपरेटिंग वैशिष्ट्यांच्या बाहेर अशा पद्धतीने करणे आवश्यक आहे. बहुधा, असे करणारी व्यक्ती बौद्धिक संपत्तीच्या चोरीमध्ये गुंतलेली असते.

- मायक्रोचिप त्यांच्या कोडच्या अखंडतेबद्दल चिंतित असलेल्या ग्राहकांसोबत काम करण्यास इच्छुक आहे.

- मायक्रोचिप किंवा इतर कोणताही सेमीकंडक्टर उत्पादक त्यांच्या कोडच्या सुरक्षिततेची हमी देऊ शकत नाही. कोड संरक्षणाचा अर्थ असा नाही की आम्ही उत्पादनाची हमी "अटूट" म्हणून देत आहोत.

कोड संरक्षण सतत विकसित होत आहे. आम्ही मायक्रोचिप येथे आमच्या उत्पादनांची कोड संरक्षण वैशिष्ट्ये सतत सुधारण्यासाठी वचनबद्ध आहोत. मायक्रोचिपचे कोड संरक्षण वैशिष्ट्य खंडित करण्याचा प्रयत्न डिजिटल मिलेनियम कॉपीराइट कायद्याचे उल्लंघन असू शकते. जर अशा कृतींमुळे तुमच्या सॉफ्टवेअरमध्ये किंवा इतर कॉपीराइट केलेल्या कामात अनधिकृत प्रवेश मिळत असेल, तर तुम्हाला त्या कायद्यांतर्गत सूट मिळविण्यासाठी दावा करण्याचा अधिकार असू शकतो.

कायदेशीर सूचना

या प्रकाशनामध्ये डिव्हाइस अॅप्लिकेशन्स आणि यासारख्या गोष्टींबाबत असलेली माहिती केवळ तुमच्या सोयीसाठी प्रदान केली आहे आणि ती अपडेट्सद्वारे बदलली जाऊ शकते. तुमचा अर्ज तुमच्या वैशिष्ट्यांशी जुळतो याची खात्री करणे तुमची जबाबदारी आहे. MICROCHIP कोणत्याही प्रकारचे कोणतेही प्रतिनिधित्व किंवा हमी देत नाही मग ते व्यक्त किंवा निहित, लिखित किंवा मौखिक, वैधानिक किंवा अन्यथा, माहितीशी संबंधित, मर्यादित नसलेल्या, मर्यादित नसलेल्या, यासह इलिलिटी किंवा उद्देशासाठी योग्यता. मायक्रोचिप ही माहिती आणि तिच्या वापरामुळे उद्भवणारी सर्व जबाबदारी नाकारते. लाइफ सपोर्ट आणि/किंवा सुरक्षा ऍप्लिकेशन्समध्ये मायक्रोचिप उपकरणांचा वापर पूर्णपणे खरेदीदाराच्या जोखमीवर आहे आणि खरेदीदार अशा वापरामुळे होणारे कोणतेही आणि सर्व नुकसान, दावे, दावे किंवा खर्चापासून निरुपद्रवी मायक्रोचिपचा बचाव, नुकसानभरपाई आणि ठेवण्यास सहमती देतो. कोणत्याही मायक्रोचिप बौद्धिक संपदा अधिकारांतर्गत कोणताही परवाना स्पष्टपणे किंवा अन्यथा सांगितल्याशिवाय दिला जात नाही.

ट्रेडमार्क

मायक्रोचिपचे नाव आणि लोगो, मायक्रोचिप लोगो, Adaptec, AnyRate, AVR, AVR लोगो, AVR Freaks, Bes Time, Bit Cloud, chip KIT, chip KIT लोगो, Crypto Memory, Crypto RF, ds PIC, Flash Flex, flex PWR HELDO, IGLOO, Jukebox, Kilo, Kleber, LAN Check, Link MD, maX Stylus, maX Touch, Media LB, मेगा AVR, मायक्रो सेमी, मायक्रो सेमी लोगो, MOST, MOST लोगो, MPLAB, Opto Lyzer, PackerTime, PIC, pico Power, PICSTART, PIC32 लोगो, Polar Fire, Prochip Designer, QTouch, SAM-BA, Sen Genuity, SpyNIC, SST, SST लोगो, SuperFlash, Symmetricom, Sync Server, Tachyon, Temp Trackr, TimeSource, tinyAVR, UNI/O, Vectron , आणि XMEGA हे यूएसए आणि इतर देशांमध्ये मायक्रोचिप टेक्नॉलॉजी इनकॉर्पोरेटेड चे नोंदणीकृत ट्रेडमार्क आहेत.

APT, ClockWorks, The Embedded Control Solutions Company, Ether Synch, Flash Tec, हायपर स्पीड कंट्रोल, हायपर लाइट लोड, Bintelli MOS, Libero, motor Bench, touch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, Pro ASIC Plus लोगो, Quiet-Wire, SmartFusion, Sync World, Timex, Time Cesium, Time Hub, Time Pictra, TimeProvider, Vite, WinPath, आणि ZL हे यूएसए मधील मायक्रोचिप तंत्रज्ञानाचे नोंदणीकृत ट्रेडमार्क आहेत.

संलग्न की सप्रेशन, AKS, analog-for-the-Digital Age, Any Capacitor, Any In, Any Out, Blue Sky, Body Com, Code Guard, Crypto Authentication, Crypto Automotive, Crypto Companion, Crypto Controller, spiced, CDEMnetds. , डायनॅमिक अॅव्हरेज मॅचिंग, DAM, ECAN, इथर ग्रीन, इन-सर्किट सिरीयल प्रोग्रामिंग, ICSP, INI Cnet, इंटर-चिप कनेक्टिव्हिटी, जिटर ब्लॉकर, क्लेबर नेट, क्लेबर नेट लोगो, मेम ब्रेन, मिंडी, Mi Wi, MPASM, MPF, MPLAB प्रमाणित लोगो, MPLIB, MPLINK, मल्टी TRAK, Net Detach, Omniscient Code Generation, PICDEM, PICDEM.net, PI चिट, PI टेल, पॉवर स्मार्ट, प्युअर सिलिकॉन, मॅट्रिक्स, REAL ICE, Ripple Blocker, SAM-ICE, Serial Quad I/O, SMART-IS, SQI, Super Switcher, Super Switcher II, Total Endurance, TSHARC, USB चेक, Vary Sense, View Span, Wiper Lock, Wireless DNA आणि ZENA हे यूएसए आणि इतर देशांमध्ये अंतर्भूत मायक्रोचिप तंत्रज्ञानाचे ट्रेडमार्क आहेत.

SQTP हे यूएसए मधील मायक्रोचिप तंत्रज्ञानाचे सेवा चिन्ह आहे

Adaptec लोगो, फ्रिक्वेन्सी ऑन डिमांड, सिलिकॉन स्टोरेज टेक्नॉलॉजी आणि Symmcom हे इतर देशांमधील Microchip Technology Inc. चे नोंदणीकृत ट्रेडमार्क आहेत.

GestIC हा मायक्रोचिप टेक्नॉलॉजी जर्मनी II GmbH & Co. KG चा नोंदणीकृत ट्रेडमार्क आहे, जो इतर देशांतील Microchip Technology Inc. ची उपकंपनी आहे.

येथे नमूद केलेले इतर सर्व ट्रेडमार्क त्यांच्या संबंधित कंपन्यांची मालमत्ता आहेत.

© 2022, Microchip Technology Incorporated, USA मध्ये मुद्रित, सर्व हक्क राखीव.

ISBN: 978-1-6683-0205-7

गुणवत्ता व्यवस्थापन प्रणाली

मायक्रोचिपच्या क्वालिटी मॅनेजमेंट सिस्टम्सच्या माहितीसाठी, कृपया भेट द्या www.microchip.com/quality.

जगभरातील विक्री आणि सेवा

कॉर्पोरेट कार्यालय

2355 वेस्ट चांडलर Blvd.

चांडलर, AZ 85224-6199

दूरध्वनी: ५७४-५३७-८९००

फॅक्स: ५७४-५३७-८९००

तांत्रिक समर्थन: www.microchip.com/support

Web पत्ता: www.microchip.com

© 2022 Microchip Technology Inc.

आणि त्याच्या उपकंपन्या अर्ज नोट

DS00003468B

कागदपत्रे / संसाधने

|

MICROCHIP AN3468 HDBaseT प्रकार 3 पॉवर्ड डिव्हाइस फ्रंट-एंड [pdf] मालकाचे मॅन्युअल AN3468 HDBaseT प्रकार 3 पॉवर्ड डिव्हाइस फ्रंट-एंड, AN3468, HDBaseT प्रकार 3 पॉवर्ड डिव्हाइस फ्रंट-एंड, पॉवर्ड डिव्हाइस फ्रंट-एंड, फ्रंट-एंड |