रेखीय तंत्रज्ञान प्रात्यक्षिक सर्किट 1255 16-बिट 25OKSPS एडीसी

वर्णन

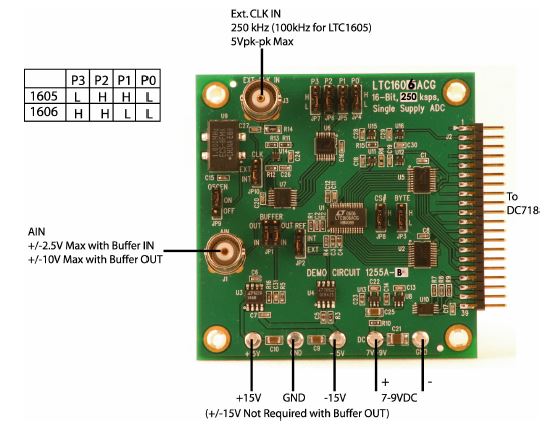

LTC1606 हा 250Ksps ADC आहे जो एका +75V पुरवठ्यातून फक्त 5mW काढतो, तर LTC1605 हा 100Ksps ADC आहे जो sin-gle +55V पुरवठ्यातून फक्त 5mW काढतो. DC1255 दोन्हीपैकी एक भाग वापरू शकतो. खालील मजकूर LTC1606 चा संदर्भ देतो परंतु तो LTC1605 ला देखील योग्य s सह लागू होतोampलिंग वारंवारता विचार. प्रात्यक्षिक सर्किट 1255 वापरकर्त्याला LTC1605/LTC1606 च्या कार्यप्रदर्शनाचे मूल्यमापन करण्याचे एक साधन प्रदान करते आणि शिफारस केलेले ग्राउंडिंग, भाग प्लेसमेंट, राउटिंग आणि बायपासिंगचे प्रदर्शन करण्याच्या उद्देशाने आहे. रचना files या सर्किट बोर्डसाठी उपलब्ध आहेत. एलटीसी कारखान्याला कॉल करा.

त्वरित प्रारंभ प्रक्रिया

कनेक्टर J1255 वापरून DC718A ला DC2B USB हायस्पीड डेटा कलेक्शन बोर्डशी कनेक्ट करा. मानक USB A/B केबलसह DC718B होस्ट पीसीशी कनेक्ट करा. 7V-9V आणि GND टर्मिनल्सवर 7V-9V DC लावा. अंतर्गत बफर वापरायचे असल्यास (डिफॉल्ट) सूचित टर्मिनलवर +15V आणि -15V लागू करा. J1 वर लो जिटर सिग्नल स्त्रोत लागू करा. घड्याळ स्रोत म्हणून, एकतर ऑनबोर्ड घड्याळ किंवा लो जिटर 250kHz 10dBm साइन वेव्ह किंवा स्क्वेअर वेव्ह ते कनेक्टर J3 वापरले जाऊ शकते. लक्षात घ्या की J3 मध्ये जमिनीवर 50• टर्मिनेशन रेझिस्टर आहे. DC51B सह पुरवलेले QuickEval-II सॉफ्टवेअर (Pscope.exe आवृत्ती K718 किंवा नंतरचे) चालवा किंवा ते येथून डाउनलोड करा. www.linear.com.

सेटअप

डीसी पॉवर

DC1255 ला 7-9VDC सुमारे 24mA आणि +/- 15V पॉवर आवश्यक आहे ampलाइफायर U3. तुम्ही U3 वापरत नसल्यास (जम्पर JP1 पहा) तुम्हाला +/-15V प्रदान करण्याची गरज नाही. 7-9VDC पुरवठा LT1761-5 रेग्युलेटर विचद्वारे ADC ला शक्ती देते अपघाती उलट पूर्वाग्रहापासून संरक्षण प्रदान करते. कनेक्शन तपशीलांसाठी आकृती 1 पहा.

घड्याळ स्त्रोत

JP10 (CLK) DC1255 इंटर-नॅली (डिफॉल्ट) आहे की बाहेरून क्लॉक केलेले आहे हे निर्धारित करते. अंतर्गत घड्याळात ECS 1MHz घड्याळ ऑसिलेटर असते, जे 74VHC161 काउंटरने विभागलेले असते. हे ऑसिल-लेटर JP9 (OSCEN) ला बंद स्थितीवर सेट करून बंद केले जाऊ शकते. जंपर्स (JP4-JP7) योग्य ADC (LTC1605 किंवा LTC1606) साठी इंटर-नल क्लॉक डिव्हायडर रेशो सेट करतात. जम्पर सेटिंग्जसाठी आकृती 1 मधील टेबल पहा. बाह्य घड्याळासाठी, तुम्ही J10 ला कमी जिटर 3dBm साइन किंवा स्क्वेअर वेव्ह प्रदान करणे आवश्यक आहे. लक्षात घ्या की J3 मध्ये जमिनीवर 50 टर्मिनेशन रेझिस्टर आहे. तर्कासह हे इनपुट चालवणे कठीण होईल. हळुवार वाढणाऱ्या कडा उच्च-च्या उपस्थितीत कनवर्टरच्या SNRशी तडजोड करू शकतात.ampलिट्यूड उच्च वारंवारता इनपुट सिग्नल. डेमो बोर्डमध्ये एज डिटेक्टर सर्किट समाविष्ट आहे पूर्ण सॉफ्टवेअर दस्तऐवजीकरण हेल्प मेनूमधून उपलब्ध आहे. टूल्स मेनूमधून अपडेट्स डाउनलोड केले जाऊ शकतात. नवीन वैशिष्ट्ये जोडली जाऊ शकतात म्हणून वेळोवेळी अद्यतने तपासा. Pscope सॉफ्टवेअरने DC1255A ओळखले पाहिजे आणि आपोआप कॉन्फिगर केले पाहिजे. डेटा प्राप्त करणे सुरू करण्यासाठी गोळा बटणावर क्लिक करा (चित्र 2 पहा). Pscope द्वारे यापूर्वी कोणता बोर्ड वापरला होता यावर अवलंबून, दुसऱ्यांदा Collect दाबणे आवश्यक असू शकते. गोळा करा बटण नंतर पॉजमध्ये बदलते, जे डेटा संपादन थांबवण्यासाठी क्लिक केले जाऊ शकते. इन्व्हर्टरचे स्वरूप (U14) त्यानंतर 200nsec विलंब, फीडिंग, मूळ घड्याळ स्त्रोतासह, दोन इनपुट NAND गेट (U7B). जर घड्याळाची उच्च वेळ 200nsec पेक्षा जास्त असेल तर हे ADC वर अंदाजे 200nsec सक्रिय कमी पल्स निर्माण करेल. 50kHz वरील 250% ड्युटी सायकल घड्याळ सामान्यत: या डेमो बोर्डांची चाचणी घेण्यासाठी वापरले जाते. शॉर्टर ड्युटी सायकल डाळी (J3 वर सक्रिय उच्च) किमान 40nsec वापरल्या जाऊ शकतात.

डेटा आउटपुट

या बोर्ड (0V-3.3V) मधील समांतर डेटा आउटपुट, DC718 शी कनेक्ट केलेले नसल्यास, लॉजिक ॲना-लायझरद्वारे प्राप्त केले जाऊ शकते आणि त्यानंतर स्प्रेडशीटमध्ये आयात केले जाऊ शकते, किंवा डिजिटल सिग्नल प्रक्रियेच्या कोणत्या स्वरूपाची इच्छा आहे त्यानुसार गणितीय पॅकेजमध्ये आयात केले जाऊ शकते.

BYTE आणि CS# जंपर्स

डेमो बोर्ड सामान्यतः BYTE (JP3) आणि CS# (JP8) जमिनीवर बांधला जातो. या ओळींचा समावेश असलेल्या फॅशनमध्ये हे उपकरण ऑपरेट करण्याचा तुमचा इरादा असल्यास, तुम्ही बाह्य स्त्रोताकडून हे सिग्नल सादर करण्याचे साधन म्हणून जंपर्स वापरू शकता.

संदर्भ

JP2 तुम्हाला ऑन चिप संदर्भ किंवा बाह्य LT1019A-2.5 (डीफॉल्ट) संदर्भ म्हणून निवडण्याची परवानगी देतो. बाह्य संदर्भाची ठराविक ड्रिफ्ट वैशिष्ट्ये ऑन चिप संदर्भासारखीच आहेत, परंतु LT1019-2.5 ने जास्तीत जास्त हमी दिली आहे.

एनालॉग इनपुट

डेमो बोर्ड JP1 सह ''IN'' पोझिशनमध्ये पाठवले जाते, या प्रकरणात, इनपुट ampलाइफायर सिग्नल मार्गावर आहे. JP1 सह ''IN'' स्थितीत, U3 (LT1468) 9dB ची वाढ प्रदान करते. हे 2.5V RMS आउटपुट लेव्हलसह सिग्नल जनरेटरला कन्व्हर्टरला पूर्ण प्रमाणात चालविण्यास अनुमती देईल. या ampलाइफायर कन्व्हर्टरच्या SNR किंवा विकृत कार्यप्रदर्शनाशी तडजोड करत नाही. LT1468 ची इनपुट आवाज घनता स्वतः 5nV/•Hz आहे. कॉन्फिगर केल्याप्रमाणे सर्किटमध्ये, फीडबॅक नेटवर्क im-pedance आणि द ampलाइफायरचे इनपुट नॉइज करंट काँ-ट्रिब्यूट नॉइज पॉवर; 7.44nV/•Hz चा इनपुट संदर्भित आवाज घनता निर्माण करण्यासाठी. 2.82 च्या वाढीसह, हे कनवर्टरद्वारे लागू केलेल्या 17kHz बँड-रुंदीमध्ये 675uV RMS आवाज निर्माण करते. हे संपूर्ण प्रमाणात 112dB चे आवाज गुणोत्तराचे सिग्नल आहे. हे अर्थातच ADC च्या आउटपुटवर सत्यापित करण्यायोग्य नाही. JP1 ''OUT'' स्थितीत असताना, J1 वर इनपुट प्रतिबाधा 10K• आहे. JP1 सह ''IN'' स्थितीत, इनपुट प्रतिबाधा खूप जास्त आहे. J1 जर 50• प्रतिबाधा चालविण्याच्या उद्देशाने जनरेटरने चालवले असेल, तर तुम्ही 50• थ्रू-टर्मिनेटर वापरू शकता. जर उच्च प्रतिबाधा स्त्रोताचे मूल्यमापन करायचे असेल, तर तुम्हाला चांगले परिणाम दिसेल ampसिग्नल मार्गातील li-fier. आपण मूल्यांकन करू इच्छित असल्यास ampयुनिटी गेनमध्ये लिफायर, R5 पुन्हा हलवा किंवा R16 च्या समांतर कमी मूल्याचा रेझिस्टर सोल्डर करा. आपण मूल्यांकन करू इच्छित असल्यास ampअधिक लाभासह लाइफायर, तुम्ही R5 चे मूल्य कमी करू शकता. तुम्ही खूप उच्च दर्जाचे रेझिस्टर वापरत असल्यास, कन्व्हर्टरचा नॉइज फ्लोअर स्पष्टपणे वाढण्यापूर्वी तुम्ही फायदा 50 पर्यंत वाढवू शकता. एक खंडtag10 च्या वाढीमुळे 90dB चा ठराविक SNR 89.9dB वर घसरला पाहिजे. एक खंडtag50 चा फायदा अंदाजे 88.7dB देईल आणि 100 चा फायदा अंदाजे 86dB SNR देईल. THD वाढेल परंतु 50 च्या वाढीसह, LT1468 चा THD अजूनही सामान्यतः -90dB च्या श्रेणीत आहे.

जर द ampलाइफायर उच्च लाभासाठी कॉन्फिगर केले आहे, तुमच्या बेंच टॉपवरील विविध साधनांमधील संभाव्य फरक डेमो बोर्डवर इनपुटमध्ये भिन्न-एंटीअल घटक विकसित करण्यासाठी आढळू शकतात. 50 च्या वाढीसह चांगले परिणाम देण्यासाठी ट्रान्सफॉर्मर अलग करणे आवश्यक असू शकते.

डेटा संकलन

डेटा संकलनासाठी वापरल्या जाणाऱ्या सिस्टीमचा डेमो बोर्डद्वारे महत्त्वपूर्ण ग्राउंड करंट निर्माण झाल्यास डेमो बोर्ड किती चांगले कार्य करते यावर नकारात्मक प्रभाव पडू शकतो. LTC6 डेटा शीटच्या पृष्ठ 1606 च्या खालच्या डावीकडे दर्शविलेल्या FFT प्लॉटची नक्कल करून हा डेमो बोर्ड तपासला जातो. यामध्ये एन्कोड घड्याळासाठी कमी जिटर, 250kHz घड्याळ स्रोत, 1KHz च्या शेजारच्या वारंवारतेवर कमी आवाज, कमी विरूपण साइनसॉइडल जनरेटर वापरणे समाविष्ट आहे. द ampघरातील चाचणीसाठी लाइफायर ''IN'' आहे आणि इनपुट सिग्नल पातळी अंदाजे -1dBfs आहे. डेटा शीटमध्ये दर्शविलेले FFT एक 4096-बिंदू FFT आहे, ज्यामध्ये इनपुट वारंवारता 1037.5976Hz आहे. ही वारंवारता 250kHz घड्याळाच्या वारंवारतेसाठी ''सुसंगत'' (विंडोमध्ये मूलभूत चक्रांची अविभाज्य संख्या तयार करते) आणि चक्रांची प्राइम संख्या (17 चक्र) असते. अविभाज्य चक्रांची मुख्य संख्या संभाव्य इनपुट कोडची सर्वात मोठी संख्या वापरते. इतर घड्याळ दरांना सुसंगत s साठी भिन्न-भिन्न इनपुट फ्रिक्वेन्सी आवश्यक आहेतampलिंग दिलेल्या s साठी इनपुट वारंवारता f ची गणना करण्यासाठीampलिंग वारंवारता fs, s ची संख्याamples n आणि अविभाज्य पूर्णांक m, खालील सूत्र वापरा.

ADC चे मूल्यमापन करताना दिशाभूल करणारे परिणाम आणू शकतील अशा अनेक परिस्थिती आहेत. एक सामान्य गोष्ट म्हणजे कन्व्हर्टरला फ्रिक्वेन्सीसह फीड करणे, ते s चे उप-मल्टिपल आहेample दर, आणि जे केवळ संभाव्य आउट-पुट कोड्सचा एक छोटा उपसंच वापरेल. तसेच, लक्षात घ्या की DC1255 मध्ये अँटी-अलायझिंग फिल्टर नाही.

जम्पर JP1 नंतर, 800kHz फर्स्ट ऑर्डर लो पास फिल्टर (R1 आणि C2) आहे. हे कनव्हर्टरच्या —3dB पॉइंटमध्ये लक्षणीय बदल करत नाही, जो सामान्यतः 675kHz असतो. म्हणून, R1 आणि C2 हे अँटी-अलायझिंग फिल्टर बनवत नाहीत. तुम्हाला तुमच्या मूल्यांकनामध्ये अँटी-अलायझिंग फिल्टरची आवश्यकता असल्यास, ते सामान्यत: LT1468 किंवा कोणत्याही बाह्य फिल्टरच्या आधी ठेवले पाहिजे ampसिग्नल मार्गातील लाइफायर. जर तुमच्याकडे फ्रिक्वेन्सी घटक असतील जे Nyquist (1/2 fs) च्या वर असतील आणि 675KHz पर्यंत आणि त्यापलीकडे असतील तर ते परत DC-125KHz बेस बँडमध्ये दुमडले जातील आणि या बँडमधील सिग्नलपासून अस्पष्ट होतील.

तुमच्याकडे फ्रिक्वेंसी अचूकतेच्या ppm पातळीसाठी सक्षम सिग्नल जनरेटर नसल्यास, तुम्ही "गळती" कमी करण्यासाठी किंवा मूलभूत गोष्टींचा प्रसार कमी करण्यासाठी विंडोिंगसह FFT वापरू शकता, कार्यप्रदर्शन पॅरामीटर्सचा अंदाजे अंदाज घेण्यासाठी. जर ए ampखराब फेज आवाजासह लाइफायर किंवा घड्याळ स्त्रोत वापरला जातो, विंडोिंग SNR सुधारणार नाही. सामान्यत: हाऊस टेस्टिंगसाठी वापरला जाणारा सिग्नल स्त्रोत B&K 1051 आहे. अंतर्गत घड्याळ स्त्रोत बहुतेक अनुप्रयोगांसाठी पुरेसा आहे. कोणत्याही उच्च कार्यक्षमता ADC प्रमाणे, हा भाग लेआउटसाठी संवेदनशील आहे. ADC च्या आजूबाजूचा परिसर हा ADC शी संबंधित विविध घटकांच्या स्थानासाठी आणि राउटिंगसाठी मार्गदर्शक-रेखा म्हणून वापरला जावा. या बोर्डच्या लेआउटमध्ये वापरलेल्या ग्राउंड प्लेनची देखील नोंद घ्यावी.

प्रात्यक्षिक सर्किट 1255

कागदपत्रे / संसाधने

|

रेखीय तंत्रज्ञान प्रात्यक्षिक सर्किट 1255 16-बिट 25OKSPS एडीसी [pdf] वापरकर्ता मार्गदर्शक 1255 16-बिट 25OKSPS एडीसी, डेमॉन्स्ट्रेशन सर्किट |