इंटेल उच्च-स्तरीय संश्लेषण कंपाइलर प्रो संस्करण

उत्पादन माहिती

| उत्पादनाचे नाव | इंटेल उच्च-स्तरीय संश्लेषण कंपाइलर प्रो संस्करण |

|---|---|

| आवृत्ती | 22.4 |

| प्रकाशन तारीख | ९ डिसेंबर २०२३ |

| अवमूल्यन सूचना | इंटेल हाय-लेव्हल सिंथेसिस कंपाइलर असण्याची योजना आहे आवृत्ती 23.4 नंतर बहिष्कृत. |

उत्पादन वापर सूचना

प्रारंभ करणे मार्गदर्शक

- तुमचे कंपाइलर वातावरण सुरू करा.

- Review विविध डिझाइन माजीampइंटेल एचएलएस कंपाइलरसह प्रदान केलेले लेस आणि ट्यूटोरियल.

वापरकर्ता मार्गदर्शक

- वापरकर्ता मार्गदर्शक सूचना प्रदान करते

- इंटेल FPGA उत्पादनांसाठी डिझाइन केलेले बौद्धिक संपदा (IP) चे संश्लेषण, पडताळणी आणि अनुकरण करणे.

- इंटेल क्वार्टस प्राइम सॉफ्टवेअरसह तुमचा घटक आयपी एका मोठ्या सिस्टीममध्ये समाकलित करण्यापर्यंत तुमचा घटक आणि टेस्टबेंच तयार करण्यापर्यंत तुमच्या घटकाच्या संपूर्ण विकास प्रवाहात जा.

सर्वोत्तम पद्धती मार्गदर्शक

सर्वोत्तम सराव मार्गदर्शक तंत्रे आणि पद्धती प्रदान करते जे तुम्ही FPGA क्षेत्राचा वापर आणि तुमच्या HLS घटकाचे कार्यप्रदर्शन सुधारण्यासाठी लागू करू शकता. तुमच्या घटकाच्या कार्यात्मक शुद्धतेची पडताळणी केल्यानंतर या सर्वोत्तम पद्धती लागू करा.

संदर्भ पुस्तिका

संदर्भ पुस्तिका Intel HLS कंपाइलरद्वारे समर्थित वैशिष्ट्यांबद्दल संदर्भ माहिती प्रदान करते. इंटेल एचएलएस कंपाइलर कमांड ऑप्शन्स, हेडर वर तपशील शोधा files, pragmas, विशेषता, मॅक्रो, घोषणा, युक्तिवाद आणि टेम्पलेट लायब्ररी.

इंटेल® हाय लेव्हल सिंथेसिस कंपाइलर प्रो एडिशन आवृत्ती 22.4 रिलीझ नोट्स

- Intel® High Level Synthesis Compiler Pro Edition Release Notes Intel High Level Synthesis Compiler Pro Edition Version 22.4 बद्दल उशीरा-ब्रेकिंग माहिती प्रदान करते.

Intel HLS कंपाइलरचे प्रलंबित अवमूल्यन

- नवीनतम FPGA उच्च-स्तरीय डिझाइन वैशिष्ट्ये, ऑप्टिमायझेशन आणि विकास उपयुक्ततांमध्ये प्रवेश ठेवण्यासाठी, Intel oneAPI बेस टूलकिट वापरण्यासाठी तुमच्या विद्यमान डिझाइन्सचे स्थलांतर करा.

- इंटेल हाय लेव्हल सिंथेसिस (HLS) कंपाइलर आवृत्ती 23.4 नंतर नापसंत करण्याची योजना आहे.

- स्थलांतर सल्ल्यासाठी इंटेल वनएपीआय उत्पादन पृष्ठाला भेट द्या किंवा कोणत्याही प्रश्नांसाठी किंवा विनंत्यांसाठी इंटेल उच्च स्तरीय डिझाइन समुदाय मंचावर जा.

इंटेल एचएलएस कंपाइलर प्रो एडिशन डॉक्युमेंटेशन लायब्ररी बद्दल

- इंटेल एचएलएस कंपाइलर प्रो एडिशनसाठी दस्तऐवजीकरण काही प्रकाशनांमध्ये विभागले गेले आहे. तुम्ही शोधत असलेली Intel HLS Compiler Pro Edition माहिती असलेले प्रकाशन शोधण्यासाठी खालील सारणी वापरा:

तक्ता 1. इंटेल हाय-लेव्हल सिंथेसिस कंपाइलर प्रो एडिशन डॉक्युमेंटेशन लायब्ररी

| शीर्षक आणि वर्णन | |

| रिलीझ नोट्स

इंटेल एचएलएस कंपाइलरबद्दल उशीरा-ब्रेकिंग माहिती प्रदान करते. |

दुवा |

| प्रारंभ करणे मार्गदर्शक

तुमचे कंपाइलर वातावरण कसे सुरू करायचे ते शिकून इंटेल एचएलएस कंपाइलरसह उठा आणि चालवाviewविविध डिझाइन माजीampइंटेल एचएलएस कंपाइलरसह प्रदान केलेले लेस आणि ट्यूटोरियल. |

दुवा |

| वापरकर्ता मार्गदर्शक

Intel FPGA उत्पादनांसाठी तुम्ही डिझाइन केलेले बौद्धिक संपदा (IP) चे संश्लेषण, पडताळणी आणि सिम्युलेट करण्याबाबत सूचना देते. इंटेल क्वार्टस प्राइम सॉफ्टवेअरसह तुमचा घटक आयपी एका मोठ्या सिस्टीममध्ये समाकलित करण्यापर्यंत तुमचा घटक आणि टेस्टबेंच तयार करण्यापर्यंत तुमच्या घटकाच्या संपूर्ण विकास प्रवाहात जा. |

दुवा |

| सर्वोत्तम पद्धती मार्गदर्शक

तुमच्या HLS घटकाचा FPGA क्षेत्र वापर आणि कार्यप्रदर्शन सुधारण्यासाठी तुम्ही लागू करू शकता अशी तंत्रे आणि पद्धती प्रदान करते. सामान्यतः, तुम्ही तुमच्या घटकाच्या कार्यात्मक शुद्धतेची पडताळणी केल्यानंतर तुम्ही या सर्वोत्तम पद्धती लागू करता. |

दुवा |

| संदर्भ पुस्तिका

Intel HLS कंपाइलरद्वारे समर्थित वैशिष्ट्यांबद्दल संदर्भ माहिती प्रदान करते. इंटेल एचएलएस कंपाइलर कमांड ऑप्शन्स, हेडर वर तपशील शोधा files, pragmas, विशेषता, मॅक्रो, घोषणा, युक्तिवाद आणि टेम्पलेट लायब्ररी. |

दुवा |

इंटेल कॉर्पोरेशन. सर्व हक्क राखीव. इंटेल, इंटेल लोगो आणि इतर इंटेल चिन्ह हे इंटेल कॉर्पोरेशन किंवा त्याच्या उपकंपन्यांचे ट्रेडमार्क आहेत. इंटेल त्याच्या FPGA आणि सेमीकंडक्टर उत्पादनांच्या कार्यप्रदर्शनास इंटेलच्या मानक वॉरंटीनुसार वर्तमान वैशिष्ट्यांनुसार वॉरंटी देते, परंतु कोणत्याही वेळी कोणतीही सूचना न देता कोणतीही उत्पादने आणि सेवांमध्ये बदल करण्याचा अधिकार राखून ठेवते. इंटेलने लिखित स्वरूपात स्पष्टपणे मान्य केल्याशिवाय येथे वर्णन केलेल्या कोणत्याही माहिती, उत्पादन किंवा सेवेच्या अर्जामुळे किंवा वापरामुळे उद्भवणारी कोणतीही जबाबदारी किंवा दायित्व स्वीकारत नाही. इंटेल ग्राहकांना कोणत्याही प्रकाशित माहितीवर विसंबून राहण्यापूर्वी आणि उत्पादने किंवा सेवांसाठी ऑर्डर देण्यापूर्वी डिव्हाइस वैशिष्ट्यांची नवीनतम आवृत्ती प्राप्त करण्याचा सल्ला दिला जातो.

*इतर नावे आणि ब्रँडवर इतरांची मालमत्ता म्हणून दावा केला जाऊ शकतो.

Intel HLS कंपाइलरचे प्रलंबित अवमूल्यन

- नवीनतम FPGA उच्च-स्तरीय डिझाइन वैशिष्ट्ये, ऑप्टिमायझेशन आणि विकास उपयुक्ततांमध्ये प्रवेश ठेवण्यासाठी, Intel oneAPI बेस टूलकिट वापरण्यासाठी तुमच्या विद्यमान डिझाइन्सचे स्थलांतर करा.

- इंटेल हाय लेव्हल सिंथेसिस (HLS) कंपाइलर आवृत्ती 23.4 नंतर नापसंत करण्याची योजना आहे.

- स्थलांतर सल्ल्यासाठी इंटेल वनएपीआय उत्पादन पृष्ठाला भेट द्या किंवा कोणत्याही प्रश्नांसाठी किंवा विनंत्यांसाठी इंटेल उच्च स्तरीय डिझाइन समुदाय मंचावर जा.

नवीन वैशिष्ट्ये आणि सुधारणा

- Intel High Level Synthesis Compiler Pro Edition Version 22.4 मध्ये खालील नवीन वैशिष्ट्ये समाविष्ट आहेत:

- देखभाल प्रकाशन.

- Intel HLS Compiler Pro Edition Version 22.4 साठी कोणतीही नवीन वैशिष्ट्ये किंवा सुधारणा नाहीत.

सॉफ्टवेअर वर्तनातील बदल

- हा विभाग इंटेल एचएलएस कंपाइलर प्रो एडिशन आवृत्ती 22.4 वैशिष्ट्ये कंपायलरच्या पूर्वीच्या रिलीझपासून बदललेली उदाहरणे देतो.

देखभाल प्रकाशन.

- Intel HLS Compiler Pro Edition Version 22.4 साठी सॉफ्टवेअर वर्तनात कोणतेही बदल नाहीत.

इंटेल हाय-लेव्हल सिंथेसिस कंपाइलर प्रो एडिशन पूर्वतयारी

- इंटेल एचएलएस कंपाइलर प्रो एडिशन इंटेल क्वार्टस® प्राइम प्रो एडिशन डिझाईन सूटचा भाग आहे. तुम्ही तुमच्या इंटेल क्वार्टस प्राइम सॉफ्टवेअर इंस्टॉलेशनचा भाग म्हणून इंटेल एचएलएस कंपाइलर इंस्टॉल करू शकता किंवा ते स्वतंत्रपणे इंस्टॉल करू शकता. वापरण्यासाठी इंटेल क्वार्टस प्राइम आणि अतिरिक्त सॉफ्टवेअर आवश्यक आहे.

- इंटेल क्वार्टस प्राइम प्रो एडिशन सॉफ्टवेअर इन्स्टॉल करण्याबाबत तपशीलवार सूचनांसाठी, सिस्टम आवश्यकता, पूर्व आवश्यकता आणि परवाना आवश्यकतांसह, इंटेल FPGA सॉफ्टवेअर इंस्टॉलेशन आणि लायसन्सिंग पहा.

- इंटेल एचएलएस कंपाइलरला इंटेल क्वार्टस प्राइम व्यतिरिक्त खालील सॉफ्टवेअरची आवश्यकता आहे:

C++ कंपाइलर

- लिनक्सवर, इंटेल एचएलएस कंपाइलरला GNU C++ लायब्ररी आणि बायनरी युटिलिटीज (binutils) सह GCC 9.3.0 आवश्यक आहे.

- GCC ची ही आवृत्ती तुमच्या Intel HLS कंपाइलर इंस्टॉलेशनचा भाग म्हणून प्रदान केली आहे. इंटेल एचएलएस कंपाइलर स्थापित केल्यानंतर, जीसीसी 9.3.0 मध्ये उपलब्ध आहे /gcc.

- महत्त्वाचे: इंटेल एचएलएस कंपाइलर वापरते /gcc निर्देशिका त्याच्या टूलचेन निर्देशिका म्हणून. तुमच्या सर्व HLS-संबंधित डिझाइन कामासाठी GCC ची ही स्थापना वापरा.

- Windows साठी, Microsoft* Visual Studio* Professional ची खालीलपैकी एक आवृत्ती स्थापित करा:

- मायक्रोसॉफ्ट व्हिज्युअल स्टुडिओ 2017 व्यावसायिक

- मायक्रोसॉफ्ट व्हिज्युअल स्टुडिओ 2017 समुदाय

- सर्वात अद्ययावत C++ 17 समर्थनासाठी, तुम्ही Visual Studio 2017 ची नवीनतम आवृत्ती वापरत असल्याची खात्री करा.

- महत्त्वाचे: Intel HLS कंपाइलर सॉफ्टवेअर सॉफ्टवेअरच्या आवृत्तीसाठी निर्दिष्ट केलेल्या व्यतिरिक्त Microsoft Visual Studio च्या आवृत्त्यांना समर्थन देत नाही.

Siemens* EDA Questa® सिम्युलेशन सॉफ्टवेअर

- विंडोज आणि रेडहॅट लिनक्स सिस्टीमवर, तुम्ही इंटेल क्वार्टस प्राइम सॉफ्टवेअर इंस्टॉलरवरून Questa® सिम्युलेशन सॉफ्टवेअर इन्स्टॉल करू शकता. उपलब्ध पर्याय खालीलप्रमाणे आहेत.

- Questa Intel FPGA संस्करण

- Questa Intel FPGA स्टार्टर संस्करण

- Questa Intel FPGA Edition आणि Questa Intel FPGA Starter Edition या दोन्हींसाठी परवाने आवश्यक आहेत. Questa Intel FPGA Starter Edition साठी परवाना विनामूल्य आहे. तपशिलांसाठी, Intel FPGA सॉफ्टवेअर इन्स्टॉलेशन आणि लायसन्सिंग पहा.

- वैकल्पिकरित्या, तुम्ही Siemens* EDA ModelSim* SE किंवा Siemens EDA Questa Advanced Simulator सॉफ्टवेअरची तुमची स्वतःची परवानाकृत आवृत्ती वापरू शकता.

- लिनक्स सिस्टमवर, Questa – Intel FPGA Edition आणि Questa – Intel FPGA Starter Edition ला Red Hat* डेव्हलपमेंट टूल्स पॅकेजेसची आवश्यकता असते.

- Intel सॉफ्टवेअर सपोर्ट करत असलेल्या सर्व ModelSim आणि Questa सॉफ्टवेअर आवृत्त्यांबद्दल माहितीसाठी, तुमच्या Intel Quartus Prime Pro Edition च्या आवृत्तीसाठी सॉफ्टवेअर आणि डिव्हाइस सपोर्ट रिलीझ नोट्समधील EDA इंटरफेस माहिती विभाग पहा.

संबंधित माहिती

- इंटेल उच्च स्तरीय संश्लेषण कंपाइलर प्रारंभ करणे मार्गदर्शक

- समर्थित ऑपरेटिंग सिस्टम

- इंटेल एफपीजीए सॉफ्टवेअर इन्स्टॉलेशन आणि लायसन्सिंग मधील सॉफ्टवेअर आवश्यकता

- ईडीए इंटरफेस माहिती (इंटेल क्वार्टस प्राइम प्रो एडिशन)

ज्ञात समस्या आणि उपाय

- हा विभाग Intel HLS Compiler Pro Edition Version 22.4 ला प्रभावित करणाऱ्या ज्ञात समस्यांबद्दल माहिती प्रदान करतो.

| वर्णन | वर्कअराउंड |

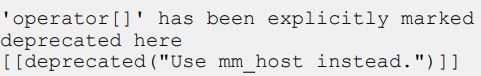

| जेव्हा तुम्ही नापसंत वर्ग mm_master वापरता, तेव्हा कंपाइलर खालीलप्रमाणे चेतावणी संदेश उत्सर्जित करतो:

हा संदेश तुमच्या कोडचा कोणता भाग बदलण्याची गरज आहे हे सूचित करत नाही. |

क्लास mm_host वापरून हा चेतावणी संदेश टाळा, जो नापसंत वर्ग mm_master बदलतो. |

| (केवळ विंडोज) लांब पथ नाव असलेल्या डिरेक्टरीमध्ये डिझाईन संकलित केल्याने कंपाइल अयशस्वी होऊ शकते.

debug.log तपासा file साठी "शोधू शकलो नाही file"त्रुटी. या त्रुटी सूचित करू शकतात की तुमचा मार्ग खूप लांब आहे. |

एका लहान पथ नावासह डिरेक्टरीमध्ये डिझाइन संकलित करा. |

| (केवळ विंडोज) तुमच्या इंटेल क्वार्टस प्राइम इन्स्टॉलेशन डिरेक्टरीचा एक लांब मार्ग तुम्हाला इंटेल एचएलएस कंपाइलर ट्युटोरियल्स यशस्वीरित्या कंपाईल आणि चालवण्यापासून रोखू शकतो आणि माजीampले डिझाईन्स.

debug.log तपासा file साठी "शोधू शकलो नाही file"त्रुटी. या त्रुटी सूचित करू शकतात की तुमचा मार्ग खूप लांब आहे. |

ट्यूटोरियल हलवा आणि उदाampत्यांना चालवण्याचा प्रयत्न करण्यापूर्वी लहान मार्गाचे नाव घ्या. |

| वर्णन | वर्कअराउंड |

| OpenCL* ला लक्ष्य करणाऱ्या आणि HLS मध्ये लिहिलेल्या लायब्ररी OpenCL कोड आणि HLS मध्ये लिहिलेल्या लायब्ररीमधील इंटरफेस म्हणून प्रवाह किंवा पाईप वापरू शकत नाहीत.

तथापि, दोन्ही अंत्यबिंदू लायब्ररीमध्ये असल्यास HLS मधील लायब्ररी प्रवाह किंवा पाईप वापरू शकते (उदा.ample, दोन टास्क फंक्शन्स जोडणारा प्रवाह). |

N/A |

| Avalon® Memory-Mapped होस्ट इंटरफेसवर ihc::maxburst पॅरामीटर लागू केल्याने तुमची रचना सिम्युलेशनमध्ये हँग होऊ शकते. | N/A |

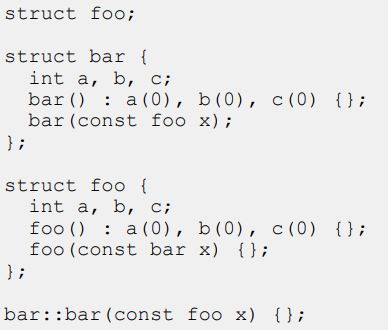

| काही असामान्य प्रकरणांमध्ये, जर तुमच्याकडे दोन वर्ग असतील ज्यांच्या कन्स्ट्रक्टरला प्रत्येकाला इनपुट म्हणून इतर वर्गाची उदाहरणे आवश्यक असतील, तर कंपाइलर क्रॅश होऊ शकतो.

उदाample, खालील कोड स्निपेट संकलित केल्याने कंपाइलर क्रॅश होतो:

|

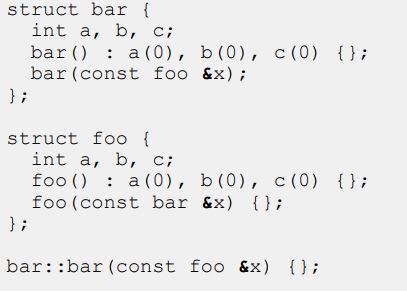

परिपत्रक व्याख्या तयार करणे टाळा. त्याऐवजी, तुमच्या कॉपी कन्स्ट्रक्टरमध्ये पॉइंटर किंवा संदर्भ वापरा.

उदाample, आधीच्या कोड स्निपेटला खालील कोडमध्ये रूपांतरित करा आणि कन्स्ट्रक्टरचा संदर्भ म्हणून स्ट्रक्टमध्ये पास करा:

|

| लायब्ररी ज्या OpenCL ला लक्ष्य करतात आणि HLS मध्ये लिहिल्या जातात त्या OpenCL कर्नलला कारणीभूत ठरू शकतात ज्यामध्ये लायब्ररीचा समावेश अधिक पुराणमतवादी वाढीव संकलन आहे. | N/A |

| लायब्ररी विकसित करताना, तुम्ही नंतर #pragma मध्ये वापरत असलेले मूल्य परिभाषित करणारे #define असल्यास, fpga_crossgen कमांड अयशस्वी होते.

उदाample, खालील कोड द्वारे संकलित केले जाऊ शकत नाही

|

#pragma ऐवजी pragma वापरा.

उदाample, खालील सह यशस्वीरित्या संकलित

|

| जेव्हा तुम्ही स्वतंत्र संकलन आणि लिंकिंग s साठी -c कमांड पर्याय वापरताtagतुमच्या वर्कफ्लोमध्ये es, आणि तुम्ही लिंकिंग s मध्ये -march पर्याय निर्दिष्ट न केल्यासtage (किंवा भिन्न -मार्च पर्याय मूल्य निर्दिष्ट करा), तुमचे लिंकिंग एसtage त्रुटी संदेशांसह किंवा त्याशिवाय अयशस्वी होऊ शकते. | -c कमांड ऑप्शन s सह संकलित करण्यासाठी तुम्ही समान -march पर्याय मूल्य वापरत असल्याची खात्री कराtage आणि लिंकिंग stage. |

| वर्णन | वर्कअराउंड |

| hls_merge मेमरी विशेषता अनरोल न केलेल्या किंवा अंशतः अनरोल केलेल्या लूपमध्ये घोषित केलेल्या ॲरेवर लागू केल्याने ॲरेच्या प्रती अनरोल केलेल्या लूप पुनरावृत्तीमध्ये विलीन केल्या जातात.

|

अनरोल केलेल्या लूपमध्ये hls_merge मेमरी विशेषता वापरणे टाळा.

तुम्हाला अनरोल केलेल्या लूपमध्ये आठवणी विलीन करायच्या असल्यास, रुंदीच्या विलीनीकरणासाठी स्ट्रक्चर प्रकाराचा ॲरे स्पष्टपणे घोषित करा किंवा डेप्थ विलीनीकरणासाठी सखोल ॲरे घोषित करा.

|

| फंक्शन मेमरी मध्ये Viewउच्च-स्तरीय डिझाइन अहवालात, काही फंक्शन-स्कोप केलेल्या आठवणी "ऑप्टिमाइझ्ड दूर" म्हणून दिसू शकतात. | काहीही नाही.

जेव्हा ए file फंक्शन्स असतात जे घटक असतात आणि फंक्शन्स असतात जे घटक नसतात, सर्व फंक्शन-स्कोप केलेले व्हेरिएबल्स फंक्शन मेमरी लिस्ट पॅनमध्ये सूचीबद्ध केले जातात, परंतु फंक्शन मेमरीमध्ये दर्शविण्यासाठी केवळ घटकांमधील व्हेरिएबल्सची माहिती असते. View फलक |

| मायक्रोसॉफ्ट इंटरनेट एक्सप्लोरर* मध्ये काही उच्च-स्तरीय डिझाइन अहवाल अयशस्वी होतात. | खालीलपैकी एक ब्राउझर वापरा view अहवाल:

• गुगल क्रोम* • मायक्रोसॉफ्ट एज* • Mozilla* Firefox* |

| पळवाट Viewउच्च-स्तरीय डिझाइन अहवालात खालील निर्बंध आहेत:

• स्टॉल-फ्री क्लस्टर्सचे वर्तन लूपमध्ये मॉडेल केलेले नाही Viewएर लूपमध्ये दर्शविलेली अंतिम विलंबता Viewस्टॉल-फ्री क्लस्टरसाठी er तुमच्या डिझाइनच्या वास्तविक विलंबापेक्षा अधिक निराशावादी (म्हणजे जास्त) आहे. क्लस्टरिंग आणि स्टॉल-फ्री क्लस्टर्सच्या वर्णनासाठी, पहा डेटापथ क्लस्टर करणे मध्ये इंटेल उच्च-स्तरीय सिंथेसिस कंपाइलर प्रो एडिशन सर्वोत्तम पद्धती मार्गदर्शक. • मेमरी किंवा प्रिंट स्टेटमेंटमधून वाचन आणि लेखनाचे स्टॉल मॉडेल केलेले नाहीत. • उच्च-पुनरावृत्ती संख्या (>1000) लूपची कार्यक्षमता कमी करते Viewएर • तुम्ही लूपमध्ये शून्य (0) ची पुनरावृत्ती संख्या निर्दिष्ट करू शकत नाही Viewएर |

काहीही नाही. |

| Windows सिस्टीमवर व्युत्पन्न केलेल्या उच्च-स्तरीय डिझाइन अहवालातील काही अहवालातील दुवे कार्य करत नाहीत. | लिनक्स प्रणालीवर उच्च-स्तरीय डिझाइन अहवाल (म्हणजे, तुमचा कोड संकलित करा) व्युत्पन्न करा. |

| पॅकेट्स वापरणाऱ्या स्टीमिंग इंटरफेसमध्ये सिंगल ac_int डेटा प्रकाराचा स्ट्रक्चर वापरणे (ihc::usesPackets ) काम करत नाही.

उदाample, खालील कोड स्निपेट कार्य करत नाही:

|

आपल्या डिझाइनमध्ये हे संयोजन वापरण्यासाठी, खालील निर्बंधांचे पालन करा:

• अंतर्गत ac_int डेटा आकार 8 च्या पटीत असणे आवश्यक आहे • प्रवाह इंटरफेस प्रकार घोषणा निर्दिष्ट करणे आवश्यक आहे ihc::bitsPerSymbol<8> उदाample, खालील कोड स्निपेट कार्य करते:

|

| वर्णन | वर्कअराउंड | |

| enqueue फंक्शन कॉल्सचा वापर करून तुमच्या घटकाचे उच्च-थ्रूपुट सिम्युलेशन चालवताना, त्या घटकासाठी सर्व ihc_hls_enqueue कॉल केल्यानंतर रांगेत असलेले घटक कॉल चालवण्यासाठी तुम्ही ihc_hls_component_run_all फंक्शन वापरत नसल्यास, खालील वर्तन घडतात:

• इम्युलेशनमध्ये, रांगेत असलेले घटक फंक्शन्स चालवले जातात. • सिम्युलेशनमध्ये, एरर किंवा चेतावणी संदेश प्रदान न करता, रांगेतील घटक कार्ये चालविली जात नाहीत. |

घटक फंक्शन कॉल रन करण्यासाठी त्या घटकासाठी सर्व ihc_hls_enqueue कॉल केल्यानंतर तुम्ही ihc_hls_component_run_all फंक्शन वापरत असल्याची खात्री करा. | |

| ihc::launch_always_run सह टास्क फंक्शन लाँच करणे | ऑप्टिमायझेशन काढून टाकणे टाळण्यासाठी, थोडा वेळ जोडा(1) | |

| कार्यासाठी लागू केलेल्या ऑप्टिमायझेशन विशेषता काढून टाकते | प्रभावित फंक्शनला लूप करून संबंधित नियंत्रण लागू करा | |

| कार्य | pragma to the while(1) लूप फंक्शन ऐवजी. | |

| खालील कोडमध्ये उदाample, फंक्शनला लागू केलेली विशेषता दुर्लक्षित केली जाते. उच्च-स्तरीय डिझाइन अहवाल या कार्यासाठी विनंती केलेल्या 1 च्या II ऐवजी 4 चा II दर्शवतात. | खालील कोड उदाampपूर्वीच्या कोडसाठी तुम्ही हा बदल कसा अंमलात आणू शकता ते दाखवाampले: | |

|

|

|

| Cyclone® V प्रकल्पांसाठी ज्यामध्ये एकाधिक HLS घटक असतात, जेव्हा तुम्ही तुमचा प्रोजेक्ट हार्डवेअरवर संकलित करण्यासाठी i++ कमांड वापरता (i++ -march=CycloneV), तेव्हा तुम्हाला त्रुटी येऊ शकते.

तुमच्या प्रोजेक्टनुसार एरर मजकूर वेगळा असला तरी, खराब व्हेरिलॉग सिंटॅक्समुळे एरर स्वाक्षरी इंटेल क्वार्टस प्राइम कंपाइलेशन अयशस्वी आहे. मॉड्यूल एक फंक्शन वापरण्याचा प्रयत्न करते जे इंटेल क्वार्टस प्राइम कंपाइलरला सापडत नाही. |

तुम्हाला ही समस्या येत असल्यास, प्रत्येक HLS घटक वेगळ्या प्रकल्पात ठेवा. | |

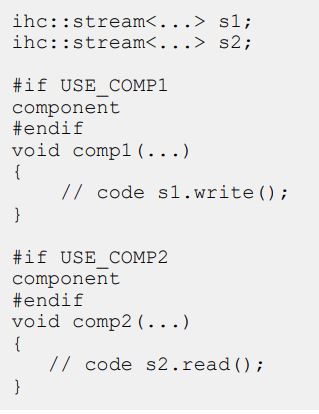

| अनेक घटक असलेल्या काही डिझाईन्सचे संकलन केल्याने प्रवाहाच्या पुनर्वापराबद्दल त्रुटी निर्माण होते. | आपल्याला ही समस्या आढळल्यास, डिझाइनमधील प्रत्येक घटक स्वतंत्रपणे संकलित करा. प्रत्येक घटक स्वतंत्रपणे संकलित करण्यासाठी सक्षम करण्यासाठी तुम्हाला तुमच्या कोडमध्ये मॅक्रो जोडण्याची आवश्यकता असू शकते. | |

| खालील उदा विचारात घ्याampले: | ||

|

||

इंटेल हाय-लेव्हल सिंथेसिस कंपाइलर प्रो एडिशन रिलीझ नोट्स संग्रहण

या वापरकर्ता मार्गदर्शकाच्या नवीनतम आणि मागील आवृत्त्यांसाठी, Intel HLS Compiler Pro Edition Release Notes पहा. सॉफ्टवेअर आवृत्ती सूचीबद्ध नसल्यास, मागील सॉफ्टवेअर आवृत्तीसाठी रिलीज नोट्स लागू होतील.

Intel HLS कंपाइलर प्रो एडिशन आवृत्ती 22.4 प्रकाशन नोट्स साठी दस्तऐवज पुनरावृत्ती इतिहास

| दस्तऐवज आवृत्ती | इंटेल क्वार्टस प्राइम आवृत्ती | बदल |

| 2022.12.19 | 22.4 | • प्रारंभिक प्रकाशनात. |

कागदपत्रे / संसाधने

|

इंटेल हाय लेव्हल सिंथेसिस कंपाइलर प्रो एडिशन [pdf] सूचना आवृत्ती 22.4, आवृत्ती 23.4, उच्च स्तरीय संश्लेषण कंपाइलर प्रो संस्करण, उच्च स्तरीय संश्लेषण कंपाइलर, प्रो संस्करण |