इंटेल एएन 805 एरिया 10 एसओसी डेव्हलपमेंट बोर्डवरील डिझाइनचे श्रेणीबद्ध आंशिक पुनर्रचना

Intel® Arria® 10 SoC विकास मंडळासाठी श्रेणीबद्ध आंशिक पुनर्रचना ट्यूटोरियल

ही ऍप्लिकेशन नोट एका साध्या डिझाईनचे पदानुक्रमाने अंशतः पुनर्रचना करता येण्याजोग्या डिझाइनमध्ये रूपांतर करणे आणि Intel® Arria® 10 SoC डेव्हलपमेंट बोर्डवर डिझाइनची अंमलबजावणी करणे दर्शवते. श्रेणीबद्ध आंशिक रीकॉन्फिगरेशन (एचपीआर) हा एक विशेष प्रकारचा आंशिक पुनर्रचना (पीआर) आहे, जिथे तुम्ही दुसर्या पीआर क्षेत्रामध्ये पीआर क्षेत्र समाविष्ट करता. तुम्ही मूल आणि पालक विभाजनांसाठी अनेक व्यक्तिरेखा तयार करू शकता. तुम्ही मूल विभाजनांना त्यांच्या पालक विभाजनांमध्ये नेस्ट करता. चाइल्ड विभाजन पुन्हा कॉन्फिगर केल्याने पालक किंवा स्थिर प्रदेशातील ऑपरेशनवर परिणाम होत नाही. पॅरेंट विभाजनाची पुनर्रचना केल्याने स्टॅटिक प्रदेशातील ऑपरेशनवर परिणाम होत नाही, परंतु मूळ विभागातील चाइल्ड विभाजने डीफॉल्ट चाइल्ड विभाजन व्यक्तिमत्वांसह बदलतात. ही पद्धत अशा प्रणालींमध्ये प्रभावी आहे जिथे एकाधिक कार्ये समान FPGA डिव्हाइस संसाधने वेळ-सामायिक करतात.

आंशिक पुनर्रचना सपाट डिझाइनमध्ये खालील प्रगती प्रदान करते:

- रन-टाइम डिझाइन रीकॉन्फिगरेशनला अनुमती देते

- डिझाइनची स्केलेबिलिटी वाढवते

- सिस्टम डाउनटाइम कमी करते

- डिझाईनमधील डायनॅमिक टाइम-मल्टीप्लेक्सिंग फंक्शन्सचे समर्थन करते

- बोर्ड जागेचा कार्यक्षम वापर करून खर्च आणि वीज वापर कमी करते

- टीप:

- या संदर्भ डिझाइनच्या अंमलबजावणीसाठी Intel Quartus® Prime FPGA अंमलबजावणी प्रवाह आणि प्राथमिक इंटेल क्वार्टस प्राइम प्रकल्पाचे ज्ञान आवश्यक आहे. files.

संबंधित माहिती

- Intel Arria 10 SoC विकास किट वापरकर्ता मार्गदर्शक

- आंशिक पुनर्रचना संकल्पना

- आंशिक पुनर्रचना डिझाइन प्रवाह

- आंशिक पुनर्रचना डिझाइन शिफारसी

- आंशिक पुनर्रचना डिझाइन विचार

संदर्भ डिझाइन आवश्यकता

या संदर्भ डिझाइनसाठी खालील गोष्टी आवश्यक आहेत:

- डिझाइन अंमलबजावणीसाठी इंटेल क्वार्टस प्राइम प्रो एडिशन सॉफ्टवेअर आवृत्ती 17.1.

- FPGA अंमलबजावणीसाठी Intel Arria 10 SoC विकास किट.

इंटेल कॉर्पोरेशन. सर्व हक्क राखीव. इंटेल, इंटेल लोगो आणि इतर इंटेल चिन्ह हे इंटेल कॉर्पोरेशन किंवा त्याच्या उपकंपन्यांचे ट्रेडमार्क आहेत. इंटेल त्याच्या FPGA आणि सेमीकंडक्टर उत्पादनांच्या कार्यप्रदर्शनास इंटेलच्या मानक वॉरंटीनुसार वर्तमान वैशिष्ट्यांनुसार वॉरंटी देते, परंतु कोणत्याही वेळी कोणतीही सूचना न देता कोणतीही उत्पादने आणि सेवांमध्ये बदल करण्याचा अधिकार राखून ठेवते. इंटेलने लिखित स्वरूपात स्पष्टपणे मान्य केल्याशिवाय येथे वर्णन केलेल्या कोणत्याही माहिती, उत्पादन किंवा सेवेच्या अर्जामुळे किंवा वापरामुळे उद्भवणारी कोणतीही जबाबदारी किंवा दायित्व स्वीकारत नाही. इंटेल ग्राहकांना कोणत्याही प्रकाशित माहितीवर विसंबून राहण्यापूर्वी आणि उत्पादने किंवा सेवांसाठी ऑर्डर देण्यापूर्वी डिव्हाइस वैशिष्ट्यांची नवीनतम आवृत्ती प्राप्त करण्याचा सल्ला दिला जातो.

- इतर नावे आणि ब्रँडवर इतरांची मालमत्ता म्हणून दावा केला जाऊ शकतो.

संदर्भ डिझाइन ओव्हरview

- या संदर्भ डिझाइनमध्ये एक 32-बिट काउंटर आहे. बोर्ड स्तरावर, डिझाइन घड्याळाला 50MHz स्त्रोताशी जोडते आणि आउटपुट FPGA वर चार LEDs शी जोडते. विशिष्ट क्रमाने काउंटर बिट्समधून आउटपुट निवडल्याने LEDs विशिष्ट वारंवारतेवर ब्लिंक होतात.

आकृती 1. पीआर विभाजनाशिवाय फ्लॅट संदर्भ डिझाइन

संदर्भ डिझाइन Files

आंशिक पुनर्रचना ट्यूटोरियल खालील ठिकाणी उपलब्ध आहे: https://github.com/intel/fpga-partial-reconfig

ट्यूटोरियल डाउनलोड करण्यासाठी:

- क्लोन क्लिक करा किंवा डाउनलोड करा.

- ZIP डाउनलोड करा वर क्लिक करा. FPGA-partial-config-master.zip अनझिप करा file.

- संदर्भ डिझाइनमध्ये प्रवेश करण्यासाठी ट्यूटोरियल्स/a10_soc_devkit_blinking_led_hpr सब-फोल्डरवर नेव्हिगेट करा.

फ्लॅट फोल्डरमध्ये खालील गोष्टींचा समावेश आहे files:

तक्ता 1. संदर्भ डिझाइन Files

| File नाव | वर्णन |

| शीर्ष एस.व्ही | वरच्या स्तरावर file डिझाइनची सपाट अंमलबजावणी समाविष्ट आहे. हे मॉड्यूल ब्लिंकिंग_लेड सब-विभाजन आणि टॉप_काउंटर मॉड्यूल इन्स्टंट करते. |

| top_counter.sv | शीर्ष-स्तरीय 32-बिट काउंटर जे थेट LED[1] नियंत्रित करते. काउंटरचे नोंदणीकृत आउटपुट LED[0] नियंत्रित करते, तसेच Blinking_led मॉड्यूलद्वारे LED[2] आणि LED[3] ला शक्ती देते. |

| blinking_led.sdc | प्रकल्पासाठी वेळेची मर्यादा परिभाषित करते. |

| चालू ठेवले… | |

| File नाव | वर्णन |

| blinking_led.SV | या ट्यूटोरियलमध्ये, तुम्ही या मॉड्यूलला पॅरेंट पीआर विभाजनामध्ये रूपांतरित करा. मॉड्यूलला top_counter मॉड्यूलचे नोंदणीकृत आउटपुट प्राप्त होते, जे LED[2] आणि LED[3] नियंत्रित करते. |

| blinking_led.qpf | इंटेल क्वार्टस प्राइम प्रकल्प file प्रकल्पातील सर्व पुनरावृत्तींची यादी असलेली. |

| blinking_led.qsf | इंटेल क्वार्टस प्राइम सेटिंग्ज file प्रकल्पासाठी असाइनमेंट आणि सेटिंग्ज समाविष्टीत. |

टीप: hpr फोल्डरमध्ये संपूर्ण संच आहे fileतुम्ही ही अॅप्लिकेशन नोट वापरून तयार करता. ह्यांचा संदर्भ घ्या fileवॉकथ्रू दरम्यान कोणत्याही टप्प्यावर s.

आकृती 2. संदर्भ डिझाइन Files

संदर्भ डिझाइन वॉकथ्रू

खालील पायऱ्या फ्लॅट डिझाइनमध्ये आंशिक पुनर्रचनाच्या अनुप्रयोगाचे वर्णन करतात. ट्यूटोरियल इंटेल अर्रिया 10 SoC विकास मंडळासाठी इंटेल क्वार्टस प्राइम प्रो एडिशन सॉफ्टवेअर वापरते:

- पायरी 1: पृष्ठ 6 वर प्रारंभ करणे

- पायरी 2: पृष्ठ 6 वर चाइल्ड लेव्हल सब-मॉड्यूल तयार करा

- पायरी 3: पृष्ठ 7 वर डिझाइन विभाजने तयार करणे

- पायरी 4: पृष्ठ 9 वर PR विभाजनांसाठी प्लेसमेंट आणि राउटिंग क्षेत्र वाटप करणे

- पायरी 5: पृष्ठ 10 वर Intel Arria 10 आंशिक रीकॉन्फिगरेशन कंट्रोलर IP कोर जोडणे

- पायरी 6: पृष्ठ 13 वर व्यक्तींची व्याख्या करणे

- पायरी 7: पृष्ठ 15 वर पुनरावृत्ती तयार करणे

- पायरी 8: पृष्ठ 20 वर श्रेणीबद्ध आंशिक पुनर्रचना प्रवाह स्क्रिप्ट तयार करणे

- पायरी 9: पृष्ठ 21 वर श्रेणीबद्ध आंशिक पुनर्रचना प्रवाह स्क्रिप्ट चालवणे

- पायरी 10: पृष्ठ 22 वर बोर्ड प्रोग्रामिंग

पायरी 1: प्रारंभ करणे

संदर्भ डिझाइन कॉपी करण्यासाठी fileतुमच्या कामाच्या वातावरणात s आणि blinking_led फ्लॅट डिझाइन संकलित करा:

- तुमच्या कार्यरत वातावरणात एक निर्देशिका तयार करा, a10_soc_devkit_blinking_led_hpr.

- डाउनलोड केलेले ट्यूटोरियल/a10_soc_devkit_blinking_led_hpr/flat सब-फोल्डर, a10_soc_devkit_blinking_led_hpr या निर्देशिकेत कॉपी करा.

- इंटेल क्वार्टस प्राइम प्रो एडिशन सॉफ्टवेअरमध्ये क्लिक करा File ➤ प्रोजेक्ट उघडा आणि blinking_led.qpf निवडा.

- फ्लॅट डिझाइन संकलित करण्यासाठी, प्रक्रिया करणे ➤ संकलन सुरू करा क्लिक करा.

पायरी 2: चाइल्ड लेव्हल सब-मॉड्यूल तयार करणे

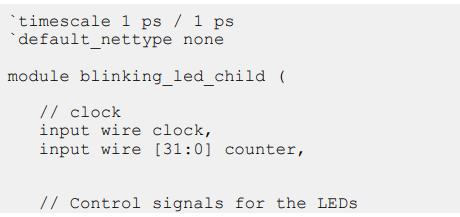

या फ्लॅट डिझाइनला श्रेणीबद्ध PR डिझाइनमध्ये रूपांतरित करण्यासाठी, तुम्ही मूल सब-मॉड्यूल (blinking_led_child. SV) तयार करणे आवश्यक आहे जे मूळ उप-मॉड्यूल (blinking_led.sv) मध्ये नेस्ट केलेले आहे.

- नवीन डिझाइन तयार करा file, blinking_led_child.sv, आणि यामध्ये खालील कोडच्या ओळी जोडा file: timescale 1 ps / 1 ps `default_nettype none module blinking_led_child ( // clock इनपुट वायर घड्याळ, इनपुट वायर [31:0] काउंटर, // LEDs साठी नियंत्रण सिग्नल

- blinking_led.sv सुधारित करा file स्टॅटिक क्षेत्रातून काउंटरच्या बिट 23 ला led_two_on कनेक्ट करण्यासाठी आणि blinking_led_child मॉड्यूल इन्स्टंट करा. बदल केल्यानंतर, तुमचे blinking_led.sv file खालीलप्रमाणे दिसणे आवश्यक आहे:

- सर्व डिझाइनमध्ये फेरफार केल्यावर files, Processing ➤ Start Compilation वर क्लिक करून प्रकल्प पुन्हा संकलित करा

पायरी 3: डिझाइन विभाजने तयार करणे

तुम्ही प्रत्येक PR क्षेत्रासाठी डिझाईन विभाजने तयार करणे आवश्यक आहे जे तुम्ही अंशतः पुन्हा कॉन्फिगर करू इच्छिता. तुम्ही तुमच्या डिझाइनमध्ये कितीही स्वतंत्र विभाजने किंवा PR क्षेत्रे तयार करू शकता. हे ट्यूटोरियल u_blinking_led_child आणि u_blinking_led उदाहरणांसाठी दोन डिझाइन विभाजने तयार करते.

श्रेणीबद्ध आंशिक पुनर्रचनासाठी डिझाइन विभाजने तयार करण्यासाठी:

- प्रोजेक्ट नेव्हिगेटरमधील u_blinking_led_child उदाहरणावर उजवे-क्लिक करा आणि डिझाईन विभाजन ➤ डिझाईन विभाजन म्हणून सेट करा क्लिक करा. विभाजन म्हणून सेट केलेल्या प्रत्येक उदाहरणाशेजारी डिझाईन विभाजन चिन्ह दिसते.

आकृती 3. प्रोजेक्ट नेव्हिगेटर पासून डिझाईन विभाजने तयार करणे

- विभाजन प्रकार परिभाषित करण्यासाठी, हायरार्की टॅबमधील u_blinking_led_child उदाहरणावर उजवे-क्लिक करा, डिझाईन विभाजन ➤ पुनर्रचना करण्यायोग्य क्लिक करा. विभाजन म्हणून उदाहरण सेट केल्यानंतरच तुम्ही विभाजन प्रकार परिभाषित करू शकता. डिझाइन विभाजन असाइनमेंटवर दिसते View डिझाईन विभाजन विंडोचा टॅब.

आकृती 4. डिझाईन विभाजन विंडो

- डिझाईन विभाजन विंडोमध्ये नावावर डबल-क्लिक करून विभाजनाचे नाव संपादित करा. या संदर्भ डिझाइनसाठी, विभाजनाचे नाव pr_partition असे पुनर्नामित करा.

टीप: जेव्हा तुम्ही विभाजन तयार करता, तेव्हा इंटेल क्वार्टस प्राइम सॉफ्टवेअर आपोआप विभाजन नाव व्युत्पन्न करते, उदाहरणाचे नाव आणि पदानुक्रम मार्गावर आधारित. हे डिफॉल्ट विभाजन नाव प्रत्येक प्रसंगानुसार बदलू शकते. - u_blinking_led उदाहरणासाठी पुनर्रचना करण्यायोग्य डिझाइन विभाजने नियुक्त करण्यासाठी चरण 1 आणि 2 पुन्हा करा. या विभाजनाला pr_parent_partition असे नाव द्या.

blinking_led.qsf मध्ये खालील असाइनमेंट आहेत याची पडताळणी करा, तुमच्या पुनर्रचना करता येण्याजोग्या डिझाईन विभाजनांशी संबंधित:

आंशिक पुनर्रचनासाठी डिझाइन विभाजने तयार करा

पायरी 4: PR विभाजनांसाठी प्लेसमेंट आणि राउटिंग क्षेत्र वाटप करणे

जेव्हा तुम्ही बेस रिव्हिजन तयार करता, तेव्हा PR डिझाईन फ्लो आरक्षित प्रदेशात संबंधित व्यक्तिमत्व कोर ठेवण्यासाठी तुमचे PR विभाजन क्षेत्र वाटप वापरतो. तुमच्या बेस रिव्हिजनसाठी डिव्हाइस फ्लोरप्लॅनमध्ये PR क्षेत्र शोधण्यासाठी आणि नियुक्त करण्यासाठी:

- प्रोजेक्ट नेव्हिगेटरमधील u_blinking_led_child उदाहरणावर उजवे-क्लिक करा आणि लॉजिक लॉक क्षेत्र क्लिक करा ➤ नवीन लॉजिक लॉक प्रदेश तयार करा. लॉजिक लॉक रीजन्स विंडोवर प्रदेश दिसतो.

- तुमच्या प्लेसमेंट क्षेत्राने blinking_led_child लॉजिक संलग्न करणे आवश्यक आहे. चिप प्लॅनरमध्ये नोड शोधून प्लेसमेंट प्रदेश निवडा. प्रोजेक्ट नेव्हिगेटरमधील u_blinking_led_child क्षेत्राच्या नावावर उजवे-क्लिक करा आणि Locate Node ➤ Locate in Chip Planner वर क्लिक करा.

आकृती 5. blinking_led साठी चिप प्लॅनर नोड स्थान

- Logic Lock Regions विंडोमध्ये, Origin कॉलममध्ये प्लेसमेंट क्षेत्र निर्देशांक निर्दिष्ट करा. मूळ प्रदेशाच्या खालच्या-डाव्या कोपर्याशी संबंधित आहे. उदाample, (X1 Y1) निर्देशांक (69 10) सह प्लेसमेंट क्षेत्र सेट करण्यासाठी, X69_Y10 म्हणून मूळ निर्दिष्ट करा. इंटेल क्वार्टस प्राइम सॉफ्टवेअर तुम्ही निर्दिष्ट केलेल्या उंची आणि रुंदीच्या आधारावर, प्लेसमेंट क्षेत्रासाठी (X2 Y2) समन्वय (वर-उजवीकडे) स्वयंचलितपणे गणना करते.

टीप: हे ट्यूटोरियल प्लेसमेंट क्षेत्रासाठी (X1 Y1) समन्वय – (69 10), आणि 20 ची उंची आणि रुंदी वापरते. स्थान नियोजन क्षेत्रासाठी कोणतेही मूल्य परिभाषित करा, जर त्या प्रदेशात blinking_led_child लॉजिक समाविष्ट असेल. - राखीव आणि फक्त कोर पर्याय सक्षम करा.

- रूटिंग क्षेत्र पर्यायावर डबल-क्लिक करा. Logic Lock Routing Region Settings डायलॉग बॉक्स दिसेल.

- राउटिंग प्रकारासाठी विस्तारासह निश्चित निवडा. हा पर्याय निवडल्याने आपोआप 1 विस्ताराची लांबी नियुक्त केली जाते.

टीप: इंजिन वेगवेगळ्या व्यक्तींना मार्ग देत असताना फिटरसाठी अतिरिक्त लवचिकता प्रदान करण्यासाठी राउटिंग क्षेत्र प्लेसमेंट क्षेत्रापेक्षा मोठा असणे आवश्यक आहे. - u_blinking_led उदाहरणासाठी चरण 1 -6 पुन्हा करा. पालक-स्तरीय प्लेसमेंट u_blinking_led उदाहरणासाठी चरण 1 -6 पुनरावृत्ती करा. पालक-स्तरीय प्लेसमेंट क्षेत्राने संबंधित बाल-स्तरीय प्लेसमेंट आणि राउटिंग क्षेत्रे पूर्णपणे संलग्न करणे आवश्यक आहे आणि पालक-स्तरीय लॉजिक प्लेसमेंटसाठी पुरेशी जागा अनुमती देते. हे ट्यूटोरियल u_blinking_led उदाहरणाच्या प्लेसमेंट क्षेत्रासाठी (X1 Y1) समन्वय – (66 7), 47 ची उंची आणि 26 ची रुंदी वापरते.

आकृती 6. लॉजिक लॉक क्षेत्र विंडो

blinking_led.qsf मध्ये तुमच्या फ्लोरप्लॅनिंगशी संबंधित खालील असाइनमेंट आहेत याची पडताळणी करा:

- आंशिक पुनर्रचना डिझाइनची फ्लोरप्लॅन

- आंशिक पुनर्रचना वाढीव अंमलबजावणी

पायरी 5: Intel Arria 10 आंशिक रीकॉन्फिगरेशन कंट्रोलर IP कोर जोडणे

- PR विभाजन पुन्हा कॉन्फिगर करण्यासाठी Intel Arria 10 आंशिक रीकॉन्फिगरेशन कंट्रोलर IP कोर वापरा. हा आयपी कोर जे वापरतोTAG PR विभाजन पुन्हा कॉन्फिगर करण्यासाठी. तुमच्या इंटेल क्वार्टस प्राइम प्रोजेक्टमध्ये Intel Arria 10 आंशिक रीकॉन्फिगरेशन कंट्रोलर IP कोर जोडण्यासाठी:

- IP कॅटलॉगमध्ये आंशिक पुनर्रचना टाइप करा.

- आयपी पॅरामीटर एडिटर प्रो विंडो लाँच करण्यासाठी, आयपी लायब्ररीमधून इंटेल एरिया 10 आंशिक पुनर्रचना कंट्रोलर आयपी कोर निवडा आणि जोडा क्लिक करा.

- नवीन आयपी व्हेरिएंट डायलॉग बॉक्समध्ये, pr_ip असे टाइप करा file नाव आणि तयार करा क्लिक करा. pr_ip साठी डीफॉल्ट पॅरामीटरायझेशन वापरा. सक्षम जेTAG डीबग मोड आणि सक्षम फ्रीझ इंटरफेस पर्याय चालू आहेत आणि Avalon-MM स्लेव्ह इंटरफेस सक्षम करा पर्याय बंद आहे.

आकृती 7. Intel Arria 10 आंशिक रीकॉन्फिगरेशन कंट्रोलर IP कोर पॅरामीटर्स

- फिनिश वर क्लिक करा आणि सिस्टम व्युत्पन्न न करता पॅरामीटर एडिटरमधून बाहेर पडा. इंटेल क्वार्टस प्राइम सॉफ्टवेअर pr_ip.ip IP भिन्नता तयार करते file, आणि जोडते file blinking_led प्रकल्पाकडे.

टीप:

- तुम्ही pr_ip.ip कॉपी करत असाल तर file hpr फोल्डरमधून, blinking_led.qsf व्यक्तिचलितपणे संपादित करा file खालील ओळ समाविष्ट करण्यासाठी: set_global_assignment -name IP_FILE pr_ip.ip

- IP_ ठेवाFILE SDC_ नंतर असाइनमेंटFILE असाइनमेंट (jtag.sdc आणि blinking_led.sdc) तुमच्या blinking_led.qsf मध्ये file. हे ऑर्डरिंग आंशिक पुनर्रचना IP कोरचे योग्य बंधन सुनिश्चित करते.

टीप: घड्याळे शोधण्यासाठी एस.डी.सी file PR IP साठी IP कोर वापरत असलेली घड्याळे तयार करणार्या कोणत्याही SDC चे अनुसरण करणे आवश्यक आहे. तुम्ही .ip ची खात्री करून ही ऑर्डर सुलभ करता file PR IP कोर कोणत्याही .ip नंतर येतो files किंवा SDC files चा वापर QSF मध्ये ही घड्याळे तयार करण्यासाठी केला जातो file तुमच्या इंटेल क्वार्टस प्राइम प्रकल्पाच्या पुनरावृत्तीसाठी. अधिक माहितीसाठी, आंशिक रीकॉन्फिगरेशन IP कोर वापरकर्ता मार्गदर्शक मधील वेळेची मर्यादा विभाग पहा.

संबंधित माहिती

- आंशिक पुनर्रचना आयपी सोल्यूशन्स वापरकर्ता मार्गदर्शक

- आंशिक रीकॉन्फिगरेशन रीजन कंट्रोलर आयपी कोरच्या माहितीसाठी.

- आंशिक पुनर्रचना IP कोर वापरकर्ता मार्गदर्शक

- वेळेच्या मर्यादांबद्दल माहितीसाठी.

शीर्ष-स्तरीय डिझाइन अद्यतनित करत आहे

Top.SV अपडेट करण्यासाठी file PR_IP उदाहरणासह:

- शीर्ष-स्तरीय डिझाइनमध्ये PR_IP उदाहरण जोडण्यासाठी, शीर्षस्थानी खालील कोड ब्लॉक अनकमेंट करा.SV file:

- रीकॉन्फिगरेशन दरम्यान आउटपुट पोर्टला लॉजिक 1 वर सक्ती करण्यासाठी, PR_IP वरून फ्रीझ कंट्रोल सिग्नल आउटपुट वापरा. तथापि, चाइल्ड विभाजनाचे PR प्रोग्रामिंग करताना पालक PR विभाजनातून LED ब्लिंक करणे सुरू ठेवण्यासाठी, फ्रीझ कंट्रोल सिग्नल led_two_on बंद करत नाही. pr_led_two_on थेट असल्याची खात्री करा

- डीफॉल्ट पॅरेंट व्यक्तिमत्वाचे (blinking_led) एक उदाहरण नियुक्त करण्यासाठी, शीर्ष अद्यतनित करा.SV file कोडच्या खालील ब्लॉकसह:

आकृती 8. आंशिक पुनर्रचना IP कोर एकत्रीकरण

पायरी 6: व्यक्तींची व्याख्या

हे संदर्भ डिझाइन पालक आणि मूल PR विभाजनांसाठी पाच स्वतंत्र व्यक्तिमत्त्वे परिभाषित करते. तुमच्या प्रकल्पातील व्यक्तिरेखा परिभाषित करण्यासाठी आणि समाविष्ट करण्यासाठी:

- चार SystemVerilog तयार करा files, blinking_led_child.sv, blinking_led_child_slow.sv, blinking_led_child_empty.sv, आणि blinking_led_slow.sv पाच व्यक्तींसाठी तुमच्या कार्यरत निर्देशिकेत.

टीप: आपण SystemVerilog तयार केल्यास fileइंटेल क्वार्टस प्राइम टेक्स्ट एडिटर वरून, अॅड अक्षम करा file चालू प्रकल्प पर्यायावर, जतन करताना files.

तक्ता 2. संदर्भ डिझाइन व्यक्ती

| File नाव | वर्णन | कोड |

| blinking_led_child.sv | बाल-स्तरीय डिझाइनसाठी डीफॉल्ट व्यक्तिमत्व |

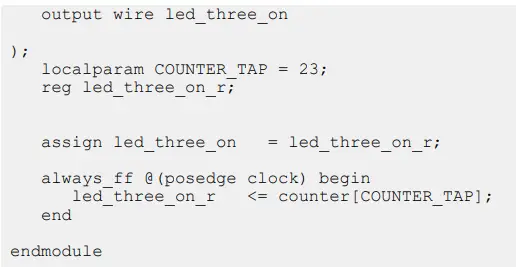

`टाइमस्केल 1 ps / 1 ps `default_nettype none module blinking_led_child ( // घड्याळ इनपुट वायर घड्याळ, इनपुट वायर [३१:०] काउंटर,

// LEDs आउटपुट वायर led_three_on साठी नियंत्रण सिग्नल

); लोकलपरम COUNTER_TAP = 23; reg led_three_on_r;

असाइन करा led_three_on = led_three_on_r; always_ff @(पोजेज घड्याळ) सुरू होते led_three_on_r <= counter[COUNTER_TAP]; शेवट

एंडमॉड्यूल |

| चालू ठेवले… | ||

| File नाव | वर्णन | कोड |

| blinking_led_child_slow.sv | द

LED_THREE हळू हळू लुकलुकते |

`टाइमस्केल 1 ps / 1 ps `default_nettype none

मॉड्यूल blinking_led_child_slow (

// घड्याळ इनपुट वायर घड्याळ, इनपुट वायर [३१:०] काउंटर,

// LEDs आउटपुट वायर led_three_on साठी नियंत्रण सिग्नल );

लोकलपरम COUNTER_TAP = 27; reg led_three_on_r;

असाइन करा led_three_on = led_three_on_r; always_ff @(पोज घड्याळ) सुरू होते led_three_on_r <= counter[COUNTER_TAP]; शेवट

एंडमॉड्यूल |

| blinking_led_child_empty.sv | द

LED_THREE चालू राहते |

`टाइमस्केल 1 ps / 1 ps `default_nettype none

मॉड्यूल blinking_led_child_empty (

// घड्याळ इनपुट वायर घड्याळ, इनपुट वायर [३१:०] काउंटर,

// LEDs आउटपुट वायर led_three_on साठी नियंत्रण सिग्नल

);

// LED सक्रिय कमी आहे असाइन करा led_three_on = 1'b0;

एंडमॉड्यूल |

| blinking_led_slow.sv | LED_TWO

हळू हळू लुकलुकते. |

`टाइमस्केल 1 ps / 1 ps `default_nettype none module blinking_led_slow( // घड्याळ इनपुट वायर घड्याळ, इनपुट वायर [३१:०] काउंटर,

// LEDs आउटपुट वायरसाठी नियंत्रण सिग्नल led_two_on, आउटपुट वायर led_three_on

);

लोकलपरम COUNTER_TAP = 27; reg led_two_on_r; असाइन करा led_two_on = led_two_on_r;

// काउंटर: नेहमी_ff @(पोजेज घड्याळ) सुरू करा led_two_on_r <= counter[COUNTER_TAP]; शेवट

blinking_led_child u_blinking_led_child( .led_three_on (led_three_on), .counter (काउंटर), .clock (घड्याळ) |

| File नाव | वर्णन | कोड |

| );ndmodule |

पायरी 3: पृष्ठ 7 वर डिझाइन विभाजने तयार करणे

पायरी 7: पुनरावृत्ती तयार करणे

PR डिझाईन फ्लो इंटेल क्वार्टस प्राइम सॉफ्टवेअरमधील प्रोजेक्ट रिव्हिजन वैशिष्ट्याचा वापर करते. तुमची सुरुवातीची रचना ही बेस रिव्हिजन आहे, जिथे तुम्ही FPGA वर स्थिर प्रदेश सीमा आणि पुनर्रचना करता येण्याजोगे प्रदेश परिभाषित करता. बेस रिव्हिजनमधून, तुम्ही अनेक रिव्हिजन तयार करता. या आवर्तनांमध्ये PR क्षेत्रांसाठी विविध अंमलबजावणी समाविष्ट आहे. तथापि, सर्व PR अंमलबजावणी पुनरावृत्ती बेस पुनरावृत्ती मधील समान शीर्ष-स्तरीय प्लेसमेंट आणि रूटिंग परिणाम वापरतात. PR डिझाइन संकलित करण्यासाठी, तुम्ही प्रत्येक व्यक्तिरेखेसाठी PR अंमलबजावणी पुनरावृत्ती आणि संश्लेषण पुनरावृत्ती तयार करणे आवश्यक आहे. या संदर्भ डिझाइनमध्ये, मूळ पुनरावृत्ती (blinking_led) व्यतिरिक्त, तीन बाल-स्तरीय व्यक्तिमत्त्व आणि दोन पालक-स्तरीय व्यक्तिमत्त्वांमध्ये पाच स्वतंत्र संश्लेषण पुनरावृत्ती आणि पाच स्वतंत्र अंमलबजावणी पुनरावृत्ती आहेत:

तक्ता 3. दोन-पालक व्यक्ती आणि तीन-मुलांच्या व्यक्तींसाठी पुनरावृत्ती

| संश्लेषण पुनरावृत्ती | अंमलबजावणी पुनरावृत्ती |

| blinking_led_parent, blinking_led_default | blinking_led_pr_alpha |

| blinking_led_parent, blinking_led_child_slow | blinking_led_pr_bravo |

| blinking_led_parent, blinking_led_child_empty | blinking_led_pr_charlie |

| blinking_led_parent_slow, blinking_led_child_slow | blinking_led_pr_delta |

| blinking_led_parent_slow, blinking_led_child_empty | blinking_led_pr_emma |

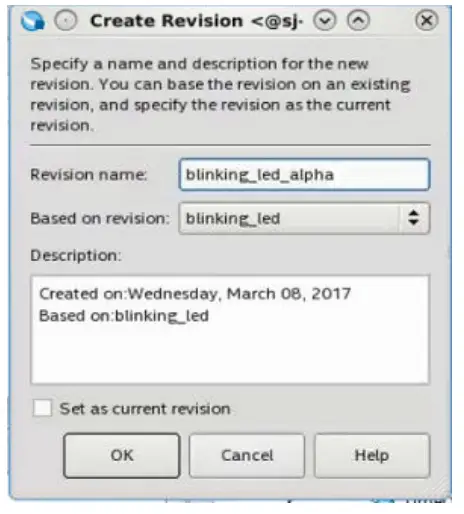

अंमलबजावणी पुनरावृत्ती तयार करणे

PR अंमलबजावणी पुनरावृत्ती तयार करण्यासाठी:

- पुनरावृत्ती डायलॉग बॉक्स उघडण्यासाठी, प्रोजेक्ट ➤ पुनरावृत्ती वर क्लिक करा.

- नवीन पुनरावृत्ती तयार करण्यासाठी, < वर डबल-क्लिक करा >.

- पुनरावृत्तीचे नाव blinking_led_pr_alpha म्हणून निर्दिष्ट करा आणि पुनरावृत्तीच्या आधारावर blinking_led निवडा.

- चालू पुनरावृत्ती पर्याय म्हणून सेट करा अक्षम करा आणि ओके क्लिक करा.

- त्याचप्रमाणे, blinking_led_pr_bravo, blinking_led_pr_charlie, blinking_led_pr_delta, आणि blinking_led_pr_emma आवर्तने, blinking_led पुनरावृत्तीवर आधारित तयार करा.

टीप: वरील आवर्तने वर्तमान पुनरावृत्ती म्हणून सेट करू नका.

आकृती 9. पुनरावृत्ती तयार करणे

संश्लेषण-केवळ आवर्तन तयार करणे

व्यक्तिमत्वांसाठी संश्लेषण-केवळ आवर्तने तयार करण्यासाठी, तुम्ही उच्च-स्तरीय घटक आणि संबंधित SystemVerilog नियुक्त करणे आवश्यक आहे. file प्रत्येक व्यक्तीसाठी:

- Intel Quartus प्राइम सॉफ्टवेअरमध्ये, Project ➤ Revisions वर क्लिक करा.

- blinking_led पुनरावृत्तीवर आधारित blinking_led_default पुनरावृत्ती तयार करा. ही पुनरावृत्ती वर्तमान पुनरावृत्ती म्हणून सेट करू नका.

- blinking_led_default.qsf मध्ये बदल करा file खालील असाइनमेंट समाविष्ट करण्यासाठी:

set_global_assignment -नाव TOP_LEVEL_ENTITY blinking_led_child

set_global_assignment -नाव SYSTEMVERILOG_FILE - त्याचप्रमाणे, blinking_led_child_slow, blinking_led_child_empty, blinking_led_parent आणि blinking_led_parent_slow आवर्तने blinking_led पुनरावृत्तीवर आधारित तयार करा. या आवर्तनांना वर्तमान आवर्तने म्हणून सेट करू नका.

- blinking_led_child_slow.qsf, blinking_led_child_empty.qsf, blinking_led_parent.qsf आणि blinking_led_parent_slow.qsf अपडेट करा files त्यांच्या अनुरूप

TOP_LEVEL_ENTITY आणि SYSTEMVERILOG_FILE असाइनमेंट:

- संश्लेषण त्रुटी टाळण्यासाठी, संश्लेषण पुनरावृत्ती सुनिश्चित करा fileचाइल्ड विभाजनांसाठी s मध्ये कोणतेही डिझाइन विभाजन, पिन असाइनमेंट किंवा लॉजिक लॉक नसतात

प्रदेश असाइनमेंट. तसेच, संश्लेषण पुनरावृत्ती fileपालक विभाजनांसाठी s मध्ये फक्त संबंधित चाइल्ड विभाजनांसाठी डिझाइन विभाजन असाइनमेंट असणे आवश्यक आहे. blinking_led_default.qsf, blinking_led_child_slow.qsf, blinking_led_child_empty.qsf, blinking_led_parent.qsf आणि blinking_led_parent_slow.pdf मधील या असाइनमेंट्स, काही असल्यास, काढून टाका. files

- blinking_led_parent.qsf आणि blinking_led_parent_slow.qsf मध्ये खालील असाइनमेंट समाविष्ट करा files:

- blinking_led.qpf तपासा file कोणत्याही विशिष्ट क्रमाने खालील आवर्तने समाविष्ट नाहीत:

- टीप: आपण पुनरावृत्ती कॉपी करत असल्यास files hpr फोल्डरमधून, blinking_led.qpf व्यक्तिचलितपणे अद्यतनित करा file कोडच्या वरील ओळींसह.

पुनरावृत्ती प्रकार निर्दिष्ट करणे

तुम्ही तुमच्या प्रत्येक आवर्तनासाठी पुनरावृत्ती प्रकार नियुक्त करणे आवश्यक आहे. तीन पुनरावृत्ती प्रकार आहेत:

- आंशिक पुनर्रचना - बेस

- आंशिक पुनर्रचना - पर्सोना संश्लेषण

- आंशिक पुनर्रचना - व्यक्तिमत्व अंमलबजावणी

- खालील सारणी प्रत्येक पुनरावृत्तीसाठी पुनरावृत्ती-प्रकार असाइनमेंट सूचीबद्ध करते:

तक्ता 4. पुनरावृत्ती प्रकार

| पुनरावृत्तीचे नाव | पुनरावृत्ती प्रकार |

| blinking_led.qsf | आंशिक पुनर्रचना - बेस |

| blinking_led_default.qsf | आंशिक पुनर्रचना - पर्सोना संश्लेषण |

| blinking_led_child_empty.qsf | आंशिक पुनर्रचना - पर्सोना संश्लेषण |

| blinking_led_child_slow.qsf | आंशिक पुनर्रचना - पर्सोना संश्लेषण |

| blinking_led_parent.qsf | आंशिक पुनर्रचना - पर्सोना संश्लेषण |

| blinking_led_parent_slow.qsf | आंशिक पुनर्रचना - पर्सोना संश्लेषण |

| blinking_led_pr_alpha.qsf | आंशिक पुनर्रचना - व्यक्तिमत्व अंमलबजावणी |

| blinking_led_pr_bravo.qsf | आंशिक पुनर्रचना - व्यक्तिमत्व अंमलबजावणी |

| blinking_led_pr_charlie.qsf | आंशिक पुनर्रचना - व्यक्तिमत्व अंमलबजावणी |

| blinking_led_pr_delta.qsf | आंशिक पुनर्रचना - व्यक्तिमत्व अंमलबजावणी |

| blinking_led_pr_emma.qsf | आंशिक पुनर्रचना - व्यक्तिमत्व अंमलबजावणी |

- प्रोजेक्ट ➤ आवर्तने वर क्लिक करा. Revisions डायलॉग बॉक्स दिसेल.

- पुनरावृत्ती नाव स्तंभात blinking_led निवडा आणि वर्तमान सेट करा वर क्लिक करा.

- लागू करा वर क्लिक करा. blinking_led पुनरावृत्ती उघडते.

- blinking_led साठी पुनरावृत्ती प्रकार सेट करण्यासाठी, असाइनमेंट ➤ सेटिंग्ज ➤ सामान्य वर क्लिक करा.

- आंशिक पुनर्रचना – बेस म्हणून पुनरावृत्ती प्रकार निवडा.

- त्याचप्रमाणे, वरील सारणीमध्ये सूचीबद्ध केल्याप्रमाणे, इतर दहा पुनरावृत्तींसाठी पुनरावृत्ती प्रकार सेट करा.

- टीप: पुनरावृत्ती प्रकार नियुक्त करण्यापूर्वी तुम्ही प्रत्येक पुनरावृत्ती वर्तमान पुनरावृत्ती म्हणून सेट करणे आवश्यक आहे. याची पडताळणी करा की प्रत्येक .qsf file खालील असाइनमेंट समाविष्ट आहे:

- टीप: तुम्ही PR अंमलबजावणी संकलित करण्यासाठी व्यक्तिमत्व अंमलबजावणी पुनरावृत्तीमध्ये वापरू इच्छित असलेल्या कोणत्याही फिटर-विशिष्ट सेटिंग्ज जोडा. फिटर-विशिष्ट सेटिंग्ज व्यक्तिरेखेच्या फिटवर परिणाम करतात, परंतु आयात केलेल्या स्थिर प्रदेशावर परिणाम करत नाहीत. तुम्ही वैयक्तिक व्यक्तिमत्व संश्लेषण पुनरावृत्तींमध्ये कोणतीही संश्लेषण-विशिष्ट सेटिंग्ज देखील जोडू शकता.

Personas साठी आवर्तने तयार करा

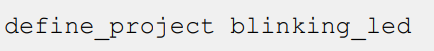

पायरी 8: श्रेणीबद्ध आंशिक पुनर्रचना प्रवाह स्क्रिप्ट व्युत्पन्न करणे

श्रेणीबद्ध आंशिक पुनर्रचना प्रवाह स्क्रिप्ट व्युत्पन्न करण्यासाठी:

- इंटेल क्वार्टस प्राइम कमांड शेलमधून, खालील कमांड चालवून फ्लो टेम्पलेट तयार करा:

- इंटेल क्वार्टस प्राइम a10_hier_partial_reconfig/flow.tcl व्युत्पन्न करते file.

- व्युत्पन्न केलेल्या a10_hier_partial_reconfig/setup.tcl.ex चे नाव बदलाampa10_hier_partial_reconfig/setup.tcl वर जा आणि तुमचे आंशिक पुनर्रचना प्रकल्प तपशील निर्दिष्ट करण्यासाठी स्क्रिप्ट सुधारित करा:

a. प्रकल्पाचे नाव परिभाषित करण्यासाठी, खालील ओळ अद्यतनित करा: b. बेस रिव्हिजन परिभाषित करण्यासाठी, खालील ओळ अपडेट करा:

b. बेस रिव्हिजन परिभाषित करण्यासाठी, खालील ओळ अपडेट करा:

- PR विभाजन नावे आणि पुनरावृत्ती लागू करणार्या स्त्रोत पुनरावृत्तीसह, प्रत्येक आंशिक पुनर्रचना अंमलबजावणी पुनरावृत्ती परिभाषित करण्यासाठी, खालील ओळी अद्यतनित करा:

टीप: सर्व पुनरावृत्ती प्रकल्प blinking_led.qpf सारख्या निर्देशिकेत असणे आवश्यक आहे. अन्यथा, त्यानुसार प्रवाह स्क्रिप्ट अद्यतनित करा.

पायरी 9: श्रेणीबद्ध आंशिक पुनर्रचना प्रवाह स्क्रिप्ट चालवित आहे

श्रेणीबद्ध आंशिक पुनर्रचना प्रवाह स्क्रिप्ट चालविण्यासाठी:

- Tools ➤ Tcl Scripts वर क्लिक करा. Tcl Scripts डायलॉग बॉक्स दिसेल.

- प्रोजेक्टमध्ये जोडा क्लिक करा, ब्राउझ करा आणि a10_hier_partial_reconfig/flow.tcl निवडा.

- लायब्ररी उपखंडात a10_hier_partial_reconfig/flow.tcl निवडा आणि Run वर क्लिक करा.

ही स्क्रिप्ट तीन व्यक्तींसाठी संश्लेषण चालवते. इंटेल क्वार्टस प्राइम एक SRAM ऑब्जेक्ट व्युत्पन्न करते File (.sof), एक आंशिक-मास्क केलेला SRAM ऑब्जेक्ट File (.pmsf), आणि रॉ बायनरी File (.rbf) प्रत्येक व्यक्तीसाठी.

टीप: इंटेल क्वार्टस प्राइम कमांड शेलमधून स्क्रिप्ट चालविण्यासाठी, खालील आदेश टाइप करा:

- आंशिक पुनर्रचना डिझाइन संकलित करा

- आंशिक पुनर्रचना प्रवाह स्क्रिप्ट वापरणे

- आंशिक पुनर्रचना प्रवाह स्क्रिप्ट कॉन्फिगर करणे

- प्रोग्रामिंग व्युत्पन्न करा Files

पायरी 10: बोर्ड प्रोग्रामिंग

आपण प्रारंभ करण्यापूर्वी:

- Intel Arria 10 SoC डेव्हलपमेंट बोर्डला वीज पुरवठा कनेक्ट करा.

- यूएसबी ब्लास्टर केबल तुमच्या PC यूएसबी पोर्ट आणि डेव्हलपमेंट बोर्डवरील यूएसबी ब्लास्टर पोर्ट दरम्यान कनेक्ट करा.

Intel Arria 10 SoC डेव्हलपमेंट बोर्डवर डिझाइन चालवण्यासाठी:

- इंटेल क्वार्टस प्राइम सॉफ्टवेअर उघडा आणि टूल्स ➤ प्रोग्रामर वर क्लिक करा.

- प्रोग्रामरमध्ये, हार्डवेअर सेटअप वर क्लिक करा आणि यूएसबी-ब्लास्टर निवडा.

- ऑटो डिटेक्ट वर क्लिक करा आणि डिव्हाइस निवडा, 10AS066N3.

- ओके क्लिक करा. इंटेल क्वार्टस प्राइम सॉफ्टवेअर बोर्डवरील तीन FPGA चिप्ससह प्रोग्रामर शोधते आणि अद्यतनित करते.

- 10AS066N3 डिव्हाइस निवडा, बदला क्लिक करा File आणि blinking_led_pr_alpha.sof लोड करा file.

- blinking_led_pr_alpha.sof साठी प्रोग्राम/कॉन्फिगर सक्षम करा file.

- प्रारंभ क्लिक करा आणि प्रगती बार 100% पर्यंत पोहोचण्याची प्रतीक्षा करा.

- मूळ फ्लॅट डिझाईन प्रमाणेच बोर्डवरील एलईडी ब्लिंक होत असल्याचे निरीक्षण करा.

- फक्त चाइल्ड पीआर क्षेत्र प्रोग्राम करण्यासाठी, blinking_led_pr_alpha.sof वर उजवे-क्लिक करा file प्रोग्रामरमध्ये आणि पीआर प्रोग्रामिंग जोडा क्लिक करा File.

- blinking_led_pr_bravo.pr_parent_partition.pr_partition.rbf निवडा file.

- blinking_led_pr_alpha.sof साठी प्रोग्राम/कॉन्फिगर अक्षम करा file.

- blinking_led_pr_bravo.pr_parent_partition.pr_partition.rbf साठी प्रोग्राम/कॉन्फिगर सक्षम करा file आणि Start वर क्लिक करा. बोर्डवर, LED[0] आणि LED[1] सतत ब्लिंक होत असल्याचे निरीक्षण करा. जेव्हा प्रोग्रेस बार 100% पर्यंत पोहोचतो, LED[2] त्याच दराने ब्लिंक होतो आणि LED[3] हळू ब्लिंक होतो.

- पालक आणि मूल PR क्षेत्र दोन्ही प्रोग्राम करण्यासाठी, .rbf वर उजवे-क्लिक करा file प्रोग्रामरमध्ये आणि पीआर प्रोग्रामिंग बदला क्लिक करा File.

- blinking_led_pr_delta.pr_parent_partition.rbf निवडा file.

- प्रारंभ क्लिक करा. बोर्डवर, LED[0] आणि LED[1] सतत लुकलुकत असल्याचे निरीक्षण करा. जेव्हा प्रगती पट्टी 100% पर्यंत पोहोचते, तेव्हा LED[2] आणि LED[3] दोन्ही हळू ब्लिंक करतात.

- फक्त चाइल्ड पीआर क्षेत्र किंवा पालक आणि बाल पीआर क्षेत्र दोन्ही एकाच वेळी डायनॅमिकरित्या पुन्हा प्रोग्राम करण्यासाठी वरील चरणांची पुनरावृत्ती करा.

आकृती 10. इंटेल एरिया 10 SoC विकास मंडळाचे प्रोग्रामिंग

विद्यमान व्यक्तिमत्व सुधारित करणे

- बेस रिव्हिजन पूर्णपणे संकलित केल्यानंतरही तुम्ही विद्यमान व्यक्तिमत्व बदलू शकता.

- उदाample, blinking_led_child_slow व्यक्तिमत्व आणखी हळू ब्लिंक करण्यासाठी:

- blinking_led_child_slow.sv मध्ये file, COUNTER_TAP पॅरामीटर 27 ते 28 पर्यंत सुधारित करा.

- हे व्यक्तिमत्व पुन्हा-संश्लेषित करण्यासाठी आणि पुन्हा लागू करण्यासाठी, तुम्ही बदलामुळे प्रभावित झालेल्या सर्व संश्लेषण-केवळ पुनरावृत्ती आणि अंमलबजावणी पुनरावृत्ती पुन्हा संकलित करणे आवश्यक आहे. खालील ओळी समाविष्ट करण्यासाठी setup.tcl स्क्रिप्टमध्ये सुधारणा करा:

टीप: blinking_led_pr_delta पुनरावृत्तीसाठी pr_parent_parition परिभाषित करताना, तुम्ही अंमलबजावणीसाठी त्या व्यक्तिरेखेचा अंतिम स्नॅपशॉट आयात करता. परिणामी, संबंधित मूल विभाजनामध्ये बदल आणि अंमलबजावणी करताना, पालक विभाजन तर्काची अंमलबजावणी समान राहते.

टीप: blinking_led_pr_delta पुनरावृत्तीसाठी pr_parent_parition परिभाषित करताना, तुम्ही अंमलबजावणीसाठी त्या व्यक्तिरेखेचा अंतिम स्नॅपशॉट आयात करता. परिणामी, संबंधित मूल विभाजनामध्ये बदल आणि अंमलबजावणी करताना, पालक विभाजन तर्काची अंमलबजावणी समान राहते. ही आज्ञा blinking_led_child_slow संश्लेषण पुनरावृत्तीचे पुन: संश्लेषण करते आणि नंतर blinking_led_pr_bravo वापरून PR अंमलबजावणी संकलित करते.

ही आज्ञा blinking_led_child_slow संश्लेषण पुनरावृत्तीचे पुन: संश्लेषण करते आणि नंतर blinking_led_pr_bravo वापरून PR अंमलबजावणी संकलित करते. - केवळ-संश्लेषण पुनरावृत्तीचे संकलन करण्यासाठी, खालील आदेश चालवा: ही आज्ञा मूळ पुनरावृत्ती पुन्हा संकलित करत नाही.

- अंमलबजावणी पुनरावृत्तीचे संकलन करण्यासाठी, खालील आदेश चालवा:

- ही कमांड बेस रिव्हिजन पुन्हा कंपाइल करत नाही.

- चरण 10 मधील चरणांचे अनुसरण करा: परिणामी RBF प्रोग्राम करण्यासाठी पृष्ठ 22 वर बोर्ड प्रोग्रामिंग करा file FPGA मध्ये.

टीप: प्रत्येक पुनरावृत्तीसाठी संपूर्ण प्रवाह चालवणे टाळण्यासाठी, setup.tcl स्क्रिप्टमध्ये संश्लेषण-केवळ पुनरावृत्ती आणि अंमलबजावणी पुनरावृत्ती परिभाषित करा आणि स्क्रिप्ट चालवा.

डिझाइनमध्ये नवीन व्यक्तिमत्व जोडत आहे

तुमची मूळ पुनरावृत्ती पूर्णपणे संकलित केल्यानंतर, तुम्ही अजूनही नवीन व्यक्ती जोडू शकता आणि वैयक्तिकरित्या या व्यक्तिरेखांचे संकलन करू शकता.

उदाample, blinking_led_parent_slow साठी नवीन बालक व्यक्तिरेखा परिभाषित करण्यासाठी, जे led_three बंद करते:

- blinking_led_child_empty.sv blinking_led_chdild_off.sv वर कॉपी करा.

- blinking_led_child_off.sv मध्ये file, असाइनमेंट सुधारित करा, असाइन करा led_three_on = 1'b0; led_three_on = 1'b1; नियुक्त करण्यासाठी. तुम्ही मॉड्यूलचे नाव blinking_led_child_empty वरून blinking_led_child_off मध्ये बदलल्याची खात्री करा.

- पृष्ठ 16 वरील संश्लेषण-केवळ पुनरावृत्ती तयार करण्याच्या चरणांचे अनुसरण करून, blinking_led_child_off, एक नवीन संश्लेषण पुनरावृत्ती तयार करा.

टीप: blinking_led_child_off पुनरावृत्ती blinking_led_child_off.sv वापरणे आवश्यक आहे file. - पृष्ठ 15 वरील अंमलबजावणी पुनरावृत्ती तयार करण्याच्या चरणांचे अनुसरण करून blinking_led_pr_foxtrot, नवीन अंमलबजावणी पुनरावृत्ती तयार करा.

- a10_hier_partial_reconfig/setup.tcl अपडेट करा file नवीन PR अंमलबजावणी परिभाषित करण्यासाठी:

- खालील आदेश चालवून फक्त हे नवीन संश्लेषण आणि अंमलबजावणी पुनरावृत्ती संकलित करा:

Intel Arria 10 उपकरणांसाठी श्रेणीबद्ध आंशिक पुनर्रचना बद्दल संपूर्ण माहितीसाठी, इंटेल क्वार्टस प्राइम प्रो एडिशन हँडबुकच्या खंड 1 मध्ये आंशिक पुनर्रचना डिझाइन तयार करणे पहा.

संबंधित माहिती

- आंशिक पुनर्रचना डिझाइन तयार करणे

- आंशिक पुनर्रचना ऑनलाइन प्रशिक्षण

दस्तऐवज पुनरावृत्ती इतिहास

तक्ता 5. दस्तऐवज पुनरावृत्ती इतिहास

| दस्तऐवज आवृत्ती | सॉफ्टवेअर आवृत्ती | बदल |

| 2017.11.06 | 17.1.0 | • अद्यतनित केले संदर्भ डिझाइन आवश्यकता सॉफ्टवेअर आवृत्तीसह विभाग

• अद्यतनित केले पीआर विभाजनाशिवाय फ्लॅट संदर्भ डिझाइन डिझाइन ब्लॉक बदलांसह आकृती • अद्यतनित केले संदर्भ डिझाइन Files वरील माहितीसह टेबल Top_counter.sv मॉड्यूल • अद्यतनित केले आंशिक पुनर्रचना IP कोर एकत्रीकरण डिझाइन ब्लॉक बदलांसह आकृती • आकडे अद्यतनित केले - डिझाईन विभाजन विंडो आणि लॉजिक लॉक क्षेत्र विंडो नवीन GUI प्रतिबिंबित करण्यासाठी • File नाव बदल • मजकूर संपादने |

| 2017.05.08 | 17.0.0 | दस्तऐवजाचे प्रारंभिक प्रकाशन |

कागदपत्रे / संसाधने

|

इंटेल एएन 805 एरिया 10 एसओसी डेव्हलपमेंट बोर्डवरील डिझाइनचे श्रेणीबद्ध आंशिक पुनर्रचना [pdf] वापरकर्ता मार्गदर्शक एरिया 805 एसओसी डेव्हलपमेंट बोर्डवरील डिझाईनचे एएन 10 श्रेणीबद्ध आंशिक पुनर्रचना, एएन 805, एरिया 10 एसओसी विकास मंडळावरील डिझाइनचे श्रेणीबद्ध आंशिक पुनर्रचना, एरिया 10 एसओसी विकास मंडळावरील डिझाइनचे पुनर्रचना, एरिया 10 एसओसी विकास मंडळ, 10 एसओसी विकास मंडळ |