इंटेल एजिलेक्स लॉजिक अॅरे ब्लॉक्स आणि अॅडॅप्टिव्ह लॉजिक मॉड्यूल्स

Intel® Agilex™ LAB आणि ALM ओव्हरview

लॉजिक अॅरे ब्लॉक (LAB) हे अॅडॉप्टिव्ह लॉजिक मॉड्यूल्स (ALMs) म्हणून ओळखल्या जाणार्या मूलभूत बिल्डिंग ब्लॉक्सचे बनलेले आहे. लॉजिक फंक्शन्स, अंकगणित फंक्शन्स आणि रजिस्टर फंक्शन्स अंमलात आणण्यासाठी तुम्ही LABs कॉन्फिगर करू शकता.

तुम्ही Intel® Agilex™ उपकरणांमध्ये उपलब्ध LABs पैकी अर्धे मेमरी LABs (MLABs) म्हणून वापरू शकता. काही उपकरणांमध्ये MLAB प्रमाण जास्त असू शकते.

Intel Quartus® Prime सॉफ्टवेअर आणि इतर समर्थित तृतीय-पक्ष संश्लेषण साधने आपोआप काउंटर, अॅडर्स, वजाबाकी आणि अंकगणित फंक्शन्स सारख्या सामान्य कार्यांसाठी योग्य मोड निवडतात.

इंटेल हायपरफ्लेक्स™ कोअर आर्किटेक्चर, इंटेल एजिलेक्स डिव्हाइस ओव्हरview

Hyper-Registers आणि Intel Hyperflex™ कोर आर्किटेक्चर बद्दल अधिक माहिती प्रदान करते. हायपर-रजिस्टर हे LAB इनपुट आणि आउटपुटशी जोडलेल्या राउटिंग सेगमेंटसह संपूर्ण कोर फॅब्रिकमध्ये प्रत्येक इंटरकनेक्ट राउटिंग विभागात उपलब्ध अतिरिक्त नोंदणी आहेत.

Intel Hyperflex™ रजिस्टर

Intel Agilex डिव्हाइस कुटुंब Intel Hyperflex™ कोर आर्किटेक्चरवर आधारित आहे.

Intel Agilex LAB मध्ये इंटेल हायपरफ्लेक्स रजिस्टर आणि इतर वैशिष्ट्ये आहेत जी रीटायमिंग सुलभ करण्यासाठी डिझाइन केलेली आहेत. इंटेल हायपरफ्लेक्स रजिस्टर्स एएलएम आणि कॅरी चेनमध्ये उपलब्ध आहेत. Intel Agilex ALM कनेक्शन तपशील आकृतीमध्ये दर्शविल्याप्रमाणे, Intel Hyperflex रजिस्टर सिंक्रोनस क्लिअरवर स्थित आहेत आणि घड्याळ मार्ग विलंब वाढवण्यासाठी किंवा कमी करण्यासाठी इनपुट सक्षम करते. सर्व इंटेल हायपरफ्लेक्स रजिस्टर्स सक्षम केले जाऊ शकतात आणि रिटाइमिंग दरम्यान इंटेल क्वार्टस प्राइम सॉफ्टवेअरद्वारे नियंत्रित केले जातात.

Intel Agilex LAB आणि ALM आर्किटेक्चर आणि वैशिष्ट्ये

खालील विभाग इंटेल एजिलेक्स उपकरणांसाठी LAB आणि ALM चे वर्णन करतात.

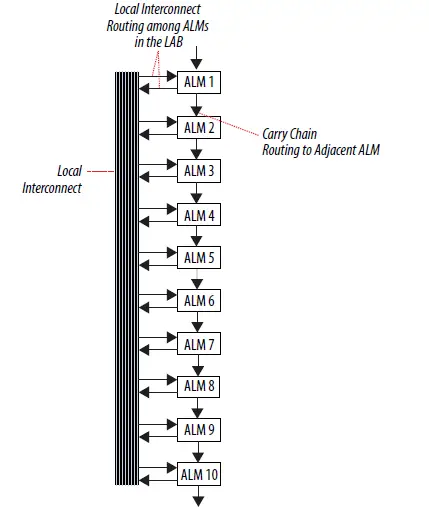

LAB

LABs हे कॉन्फिगर करण्यायोग्य लॉजिक ब्लॉक्स आहेत ज्यात लॉजिक संसाधनांचा समूह असतो. प्रत्येक LAB मध्ये त्याच्या ALM ला ड्रायव्हिंग कंट्रोल सिग्नलसाठी समर्पित लॉजिक असते. MLAB हा LAB चा एक सुपरसेट आहे आणि त्यात LAB च्या सर्व वैशिष्ट्यांचा समावेश आहे. Intel Agilex LAB आणि MLAB स्ट्रक्चर आकृतीमध्ये दाखवल्याप्रमाणे प्रत्येक LAB मध्ये एकूण 10 ALM आहेत.

आकृती 1.

Intel Agilex LAB स्ट्रक्चर आणि इंटरकनेक्ट्स ओव्हरview

ही आकृती एक ओव्हर दर्शवतेview Intel Agilex LAB आणि MLAB ची रचना LAB एकमेकांशी जोडलेली आहे.

संबंधित माहिती

संबंधित माहिती

पान 6 वर MLAB

आमदार बी

प्रत्येक MLAB कमाल 640 बिट्स साध्या ड्युअल-पोर्ट SRAM चे समर्थन करते. तुम्ही प्रत्येक ALM ला 32 (खोली) x 2 (रुंदी) मेमरी ब्लॉक म्हणून एका MLAB मध्ये कॉन्फिगर करू शकता, परिणामी 32 (खोली) x 20 (रुंदी) साध्या ड्युअल-पोर्ट SRAM ब्लॉकचे कॉन्फिगरेशन होईल.

आकृती 2.

Intel Agilex LAB आणि MLAB स्ट्रक्चर स्थानिक आणि थेट लिंक इंटरकनेक्ट

स्थानिक आणि थेट लिंक इंटरकनेक्ट

प्रत्येक LAB 60 ALM आउटपुट काढू शकते. यापैकी एक उपसंच थेट LAB इनपुट चालवू शकतो, परंतु भिन्न पंक्ती किंवा स्तंभाशी असलेले कोणतेही कनेक्शन किमान एक सामान्य-उद्देश रूटिंग वायर वापरणे आवश्यक आहे.

स्थानिक इंटरकनेक्ट ALM इनपुट चालवते. ALM आउटपुट, तसेच स्तंभ आणि पंक्ती इंटरकनेक्ट स्थानिक इंटरकनेक्ट चालवतात.

आकृती 3. Intel Agilex LAB स्थानिक आणि थेट लिंक इंटरकनेक्ट  कॅरी चेन इंटरकनेक्ट्स

कॅरी चेन इंटरकनेक्ट्स

ALM मध्ये एक समर्पित कॅरी चेन मार्ग आहे. इंटेल एजिलेक्स उपकरणांमध्ये कार्यक्षम अंकगणितीय कार्यांसाठी कॅरी चेन राउटिंग करण्यासाठी LABs मध्ये वर्धित इंटरकनेक्ट संरचना समाविष्ट आहे. हे ALM-ते-ALM कनेक्शन स्थानिक इंटरकनेक्टला बायपास करतात.

इंटेल हायपरफ्लेक्स रजिस्टर्स कॅरी चेनमध्ये जोडले जातात ज्यामुळे LABs च्या साखळीमध्ये लवचिक रिटाइमिंग सक्षम होते आणि इंटेल क्वार्टस प्राइम कंपाइलर आपोआप अॅडव्हान घेते.tage या संसाधनांचा वापर आणि कार्यप्रदर्शन सुधारण्यासाठी.

आकृती 4. कॅरी चेन इंटरकनेक्ट्स LAB नियंत्रण सिग्नल

LAB नियंत्रण सिग्नल

प्रत्येक LAB कंट्रोल ब्लॉकमध्ये दोन घड्याळ स्रोत आहेत, जे LAB मध्ये ALM रजिस्टर्स आणि हायपर-रजिस्टर चालवण्यासाठी दोन LAB घड्याळे (LABCLK[1:0]) आणि दोन विलंबित LAB घड्याळे (LABCLK_Phi1[1:0]) तयार करतात. LAB दोन अनन्य घड्याळ सक्षम सिग्नल, तसेच ALM नोंदणीसाठी अतिरिक्त स्पष्ट संकेतांना समर्थन देते.

LAB पंक्ती घड्याळे [5..0] आणि LAB लोकल इंटरकनेक्ट्स LAB-व्यापी नियंत्रण सिग्नल तयार करतात. कमी स्क्यू क्लॉक नेटवर्क पंक्तीच्या घड्याळांना जागतिक सिग्नल वितरीत करते [५..०]. मल्टीट्रॅक इंटरकनेक्टमध्ये राउटिंग कार्यक्षमतेसाठी वापरल्या जाणार्या वेगवेगळ्या लांबीच्या आणि वेगाच्या सतत, कार्यप्रदर्शन-अनुकूलित राउटिंग लाइन्स असतात. इंटेल क्वार्टस प्राइम कंपाइलर डिझाईन कार्यप्रदर्शन सुधारण्यासाठी आणि डिव्हाइस संसाधने ऑप्टिमाइझ करण्यासाठी जलद इंटरकनेक्ट्सवर आपोआप गंभीर डिझाइन मार्गांना रूट करते.

तर्कशास्त्र नियंत्रण साफ करा

LAB-व्यापी सिग्नल ALM रजिस्टरच्या स्पष्ट सिग्नलसाठी तर्क नियंत्रित करतात. ALM रजिस्टर सिंक्रोनस आणि अॅसिंक्रोनस क्लिअर या दोन्हींना थेट समर्थन देते. प्रत्येक LAB एक समकालिक स्पष्ट सिग्नल आणि दोन असिंक्रोनस स्पष्ट संकेतांना समर्थन देते.

Intel Agilex डिव्हाइसेस डिव्हाइस-व्यापी रीसेट पिन (DEV_CLRn) प्रदान करतात जे डिव्हाइसमधील सर्व नोंदणी रीसेट करतात. संकलित करण्यापूर्वी तुम्ही इंटेल क्वार्टस प्राइम सॉफ्टवेअरमध्ये DEV_CLRn पिन सक्षम करू शकता. डिव्हाइस-व्यापी रीसेट सिग्नल इतर सर्व नियंत्रण सिग्नल ओव्हरराइड करते.

आकृती 5. Intel Agilex LAB-वाइड कंट्रोल सिग्नल

ALM

खालील विभागांमध्ये ALM संसाधने, ALM आउटपुट आणि ALM ऑपरेटिंग मोड समाविष्ट आहेत.

ALM संसाधने

प्रत्येक ALM मध्ये विविध LUT-आधारित संसाधने असतात जी दोन कॉम्बिनेशनल अॅडॉप्टिव्ह LUTs (ALUTs), दोन-बिट्स फुल अॅडर आणि चार रजिस्टर्समध्ये विभागली जाऊ शकतात.

दोन कॉम्बिनेशनल ALUT साठी आठ इनपुट्ससह, एक ALM दोन फंक्शन्सच्या विविध संयोजनांची अंमलबजावणी करू शकतो. ही अनुकूलता ALM ला चार इनपुट LUT आर्किटेक्चरसह पूर्णपणे बॅकवर्ड-सुसंगत होण्यास अनुमती देते. एक ALM आठ इनपुट फंक्शन्सचा उपसंच देखील लागू करू शकतो.

एका ALM मध्ये चार प्रोग्राम करण्यायोग्य रजिस्टर असतात. प्रत्येक रजिस्टरमध्ये खालील पोर्ट असतात:

- मध्ये डेटा

- डेटा बाहेर

- सामान्य LAB घड्याळ

- विलंबित LAB घड्याळ

- घड्याळ सक्षम

- समकालिक स्पष्ट

- असिंक्रोनस स्पष्ट

ग्लोबल सिग्नल्स, सामान्य-उद्देश I/O (GPIO) पिन किंवा कोणतेही अंतर्गत लॉजिक हे घड्याळ सक्षम सिग्नल, घड्याळ आणि ALM रजिस्टरचे असिंक्रोनस किंवा सिंक्रोनस स्पष्ट नियंत्रण सिग्नल चालवू शकतात. घड्याळ सक्षम सिग्नलला सिंक्रोनस रीसेट सिग्नलपेक्षा प्राधान्य आहे.

कॉम्बिनेशनल फंक्शन्ससाठी, रजिस्टर्स बायपास केले जातात आणि लुक-अप टेबल (LUT) आणि अॅडर्सचे आउटपुट थेट ALM च्या आउटपुटवर जाते. आउटपुट म्यूक्सला बायपास करण्यासाठी आणि गंभीर पथ समायोजनासाठी दुसऱ्या LAB शी कनेक्ट करण्यासाठी 6 LUT आउटपुट आणि तळाशी 5 LUT आउटपुटसाठी दोन जलद आउटपुट उपलब्ध आहेत.

आकृती 6. Intel Agilex ALM उच्च-स्तरीय ब्लॉक आकृती

ALM आउटपुट

ALM आउटपुट

प्रत्येक ALM मधील सामान्य राउटिंग आउटपुट स्थानिक, पंक्ती आणि स्तंभ राउटिंग संसाधने चालवतात. दोन जलद आउटपुट पथांसह सहा ALM आउटपुट, स्तंभ, पंक्ती किंवा थेट लिंक रूटिंग कनेक्शन चालवू शकतात.

LUT, adder किंवा रजिस्टर आउटपुट ALM आउटपुट चालवू शकतात. LUT किंवा adder आणि ALM रजिस्टर दोन्ही एकाच वेळी ALM मधून बाहेर काढू शकतात.

रजिस्टर पॅकिंग असंबंधित रजिस्टर आणि कॉम्बिनेशनल लॉजिकला एकाच ALM मध्ये पॅक करण्याची परवानगी देऊन डिव्हाइस वापर सुधारते. ALM LUT किंवा अॅडर आउटपुटच्या नोंदणीकृत आणि नोंदणीकृत नसलेल्या आवृत्त्या देखील काढू शकते.

खालील आकृती Intel Agilex ALM कनेक्टिव्हिटी दाखवते. इंटेल क्वार्टस प्राइम रिसोर्स प्रॉपर्टी एडिटरमध्ये, संपूर्ण ALM कनेक्शन सरलीकृत केले आहे. इंटेल क्वार्टस प्राइम सॉफ्टवेअरद्वारे काही राउटिंग्स आंतरिकरित्या रूट केल्या जातील.

आकृती 7. Intel Agilex ALM कनेक्शन तपशील ALM ऑपरेटिंग मोड्स

ALM ऑपरेटिंग मोड्स

Intel Agilex ALM खालीलपैकी कोणत्याही मोडमध्ये कार्य करते:

- सामान्य मोड

- विस्तारित LUT मोड

- अंकगणित मोड

सामान्य मोड

सामान्य मोड एका Intel Agilex ALM मध्ये दोन फंक्शन्स किंवा सहा इनपुट पर्यंत एक फंक्शन लागू करण्याची परवानगी देतो.

LAB लोकल इंटरकनेक्ट मधील आठ डेटा इनपुट हे कॉम्बिनेशनल लॉजिकचे इनपुट आहेत.

ALM पूर्णपणे स्वतंत्र फंक्शन्स आणि सामान्य इनपुट असलेल्या फंक्शन्सच्या विविध संयोजनांना समर्थन देऊ शकते.

इंटेल क्वार्टस प्राइम कंपाइलर स्वयंचलितपणे LUT साठी इनपुट निवडतो. सामान्य मोडमधील ALMs नोंदणी पॅकिंगला समर्थन देतात.

खालील आकृती LUT मोडसाठी भिन्न इनपुट कनेक्शनचे संयोजन दर्शवते. तुमच्या डिझाईनमध्ये, इंटेल क्वार्टस प्राइम सॉफ्टवेअर संकलनादरम्यान वेगवेगळे इनपुट नेमिंग देऊ शकते.

आकृती 8. सामान्य मोडमध्ये ALM

दर्शविलेल्या पेक्षा कमी इनपुटसह फंक्शन्सचे संयोजन देखील समर्थित आहेत. उदाample, खालील इनपुटच्या संख्येसह फंक्शन्सचे संयोजन समर्थित आहेत.

- 4 आणि 3

- 3 आणि 3

- 3 आणि 2

- 5 आणि 2

एका ALM मध्ये दोन 5-इनपुट फंक्शन्स पॅक करण्यासाठी, फंक्शन्समध्ये किमान दोन सामान्य इनपुट असणे आवश्यक आहे. डेटा आणि डेटाबेस हे सामान्य इनपुट आहेत. 4-इनपुट फंक्शनसह 5-इनपुट फंक्शनच्या संयोजनासाठी एक सामान्य इनपुट (डेटा किंवा डेटाब) आवश्यक आहे.

विरळ वापरल्या जाणार्या उपकरणामध्ये, सर्वोत्तम संभाव्य कामगिरी साध्य करण्यासाठी इंटेल क्वार्टस प्राइम सॉफ्टवेअरद्वारे एका ALM मध्ये ठेवता येणारी कार्ये वेगळ्या ALM मध्ये लागू केली जाऊ शकतात. एक उपकरण भरण्यास सुरुवात झाल्यावर, इंटेल क्वार्टस प्राइम सॉफ्टवेअर आपोआप Intel Agilex ALM ची पूर्ण क्षमता वापरते. इंटेल क्वार्टस प्राइम कंपाइलर सामान्य इनपुट वापरून फंक्शन्स शोधतो किंवा डिव्हाइस संसाधनांचा कार्यक्षम वापर करण्यासाठी एका ALM मध्ये ठेवण्यासाठी पूर्णपणे स्वतंत्र कार्ये शोधतो. याव्यतिरिक्त, तुम्ही स्थान असाइनमेंट सेट करून संसाधनाचा वापर व्यक्तिचलितपणे नियंत्रित करू शकता.

आकृती 9. 6-इनपुट LUT मोड फंक्शन सामान्य मोडमध्ये

आकृती 10. 3-इनपुट LUT मोड फंक्शन सामान्य मोडमध्ये

आकृती 10. 3-इनपुट LUT मोड फंक्शन सामान्य मोडमध्ये

डेटा आणि डेटा बी रजिस्टर पॅकिंगसाठी उपलब्ध आहेत.  तुम्ही खालील इनपुट वापरून कोणतेही तीन ते सहा इनपुट फंक्शन लागू करू शकता:

तुम्ही खालील इनपुट वापरून कोणतेही तीन ते सहा इनपुट फंक्शन लागू करू शकता:

- डेटा

- datad0

- datac0

- datac1

- datad1

- dataf

- dataa आणि datab — ज्याद्वारे प्रत्येक LUT मध्ये भिन्न कार्य कार्यान्वित करण्यासाठी लवचिकता प्रदान करण्यासाठी दोन्ही LUT मध्ये dataa आणि datab सामायिक केले जातात.

डेटा आणि डाटाब इनपुट दोन्ही रजिस्टर पॅकिंग वैशिष्ट्यास समर्थन देतात. तुम्ही रजिस्टर पॅकिंग वैशिष्ट्य सक्षम केल्यास, डेटा आणि डाटाब इनपुट किंवा दोन्हीपैकी एक इनपुट LUT ला बायपास करून थेट रजिस्टरमध्ये फीड करतात, वापरलेल्या पॅक केलेल्या रजिस्टर मोडवर अवलंबून. Intel Agilex उपकरणांसाठी, खालील प्रकारचे पॅक केलेले रजिस्टर मोड समर्थित आहेत:

- 5 पॅक केलेल्या नोंदणी मार्गासह 1-इनपुट LUT

- 5 पॅक केलेल्या नोंदणी पथांसह 2-इनपुट LUT

- 3 पॅक केलेल्या नोंदणी पथांसह दोन 2-इनपुट LUT

3-इनपुट LUT 2 पॅक्ड रजिस्टर पथांसह सामान्य मोड आकृतीमध्ये 3-इनपुट LUT मोड फंक्शनमध्ये स्पष्ट केले आहे. Intel Agilex उपकरणांसाठी, 6-इनपुट LUT मोड रजिस्टर पॅकिंग वैशिष्ट्याला समर्थन देत नाही.

विस्तारित LUT मोड

आकृती 11. विस्तारित LUT मोडमध्ये समर्थित 8-इनपुट कार्ये

सर्व LUT इनपुट वापरून विशिष्ट 8-इनपुट फंक्शन्स एकाच ALM मध्ये लागू केली जाऊ शकतात:

- डेटा

- datad0

- datac0

- डेटा

- डेटाब

- datac1

- datad1

- dataf

8-इनपुट विस्तारित LUT मोडमध्ये, पॅक केलेले रजिस्टर मोड समर्थित आहे, जर पॅक केलेले रजिस्टर 8-इनपुट LUT सह डेटा किंवा डेटाबेस इनपुट सामायिक करते.

अंकगणित मोड

अंकगणित मोडमधील ALM दोन समर्पित पूर्ण अॅडर्ससह दोन 4-इनपुट LUT चे दोन संच वापरते. समर्पित अॅडर्स LUT ला प्री-अॅडर लॉजिक करण्यास परवानगी देतात. म्हणून, प्रत्येक अॅडर दोन 4-इनपुट फंक्शन्सचे आउटपुट जोडू शकतो.

अंकगणित मोड देखील घड्याळ सक्षम, काउंटर सक्षम, समकालिक वर आणि खाली नियंत्रण, नियंत्रण जोडा आणि वजा, आणि समकालिक स्पष्ट ऑफर करतो.

स्पष्ट आणि घड्याळ सक्षम पर्याय हे LAB-व्यापी सिग्नल आहेत जे LAB मधील सर्व नोंदणींना प्रभावित करतात. अॅडॉप्टिव्ह LUT (ALUT) मधील रजिस्टरच्या प्रत्येक जोडीसाठी तुम्ही स्वतंत्रपणे हे सिग्नल अक्षम किंवा सक्षम करू शकता. इंटेल क्वार्टस प्राइम सॉफ्टवेअर इतर LAB मध्ये काउंटरद्वारे वापरलेले नसलेले कोणतेही रजिस्टर आपोआप ठेवते.

आकृती 12. अंकगणित मोडमध्ये Intel Agilex ALM

साखळी घेऊन जा

साखळी घेऊन जा

कॅरी चेन अंकगणित मोडमध्ये समर्पित अॅडर्स दरम्यान जलद कॅरी फंक्शन प्रदान करते.

इंटेल एजिलेक्स उपकरणांमधील 2-बिट कॅरी सिलेक्ट वैशिष्ट्य ALM सह कॅरी चेनच्या प्रसार विलंबाचे विभाजन करते. कॅरी चेन पहिल्या ALM किंवा LAB मधील सहाव्या ALM मध्ये सुरू होऊ शकतात. अंतिम कॅरी-आउट सिग्नल ALM कडे पाठवला जातो, जिथे तो स्थानिक, पंक्ती किंवा स्तंभ एकमेकांशी जोडला जातो.

इंटेल एजिलेक्स लॉजिक अॅरे ब्लॉक्स आणि अॅडॅप्टिव्ह लॉजिक मॉड्यूल्स वापरकर्ता मार्गदर्शकासाठी दस्तऐवज पुनरावृत्ती इतिहास

| दस्तऐवज आवृत्ती | बदल |

| 2022.05.24 | अद्यतनित आकृती: Intel Agilex ALM उच्च-स्तरीय ब्लॉक आकृती. |

| 2019.11.14 | LAB नियंत्रण सिग्नल विभागातील वर्णन अद्यतनित केले. |

| 2019.10.01 |

|

| 2019.04.02 | प्रारंभिक प्रकाशन. |

इंटेल कॉर्पोरेशन.

सर्व हक्क राखीव. इंटेल, इंटेल लोगो आणि इतर इंटेल चिन्ह हे इंटेल कॉर्पोरेशन किंवा त्याच्या उपकंपन्यांचे ट्रेडमार्क आहेत. इंटेल त्याच्या FPGA आणि सेमीकंडक्टर उत्पादनांच्या कार्यप्रदर्शनास इंटेलच्या मानक वॉरंटीनुसार वर्तमान वैशिष्ट्यांनुसार वॉरंटी देते, परंतु कोणत्याही वेळी कोणतीही सूचना न देता कोणतीही उत्पादने आणि सेवांमध्ये बदल करण्याचा अधिकार राखून ठेवते. इंटेलने लिखित स्वरूपात स्पष्टपणे मान्य केल्याशिवाय येथे वर्णन केलेल्या कोणत्याही माहिती, उत्पादन किंवा सेवेच्या अर्जामुळे किंवा वापरामुळे उद्भवणारी कोणतीही जबाबदारी किंवा दायित्व स्वीकारत नाही. इंटेल ग्राहकांना कोणत्याही प्रकाशित माहितीवर विसंबून राहण्यापूर्वी आणि उत्पादने किंवा सेवांसाठी ऑर्डर देण्यापूर्वी डिव्हाइस वैशिष्ट्यांची नवीनतम आवृत्ती प्राप्त करण्याचा सल्ला दिला जातो.

*इतर नावे आणि ब्रँडवर इतरांची मालमत्ता म्हणून दावा केला जाऊ शकतो.

आयएसओ

१६:१०

नोंदणीकृत

कागदपत्रे / संसाधने

|

इंटेल एजिलेक्स लॉजिक अॅरे ब्लॉक्स आणि अॅडॅप्टिव्ह लॉजिक मॉड्यूल्स [pdf] वापरकर्ता मार्गदर्शक एजिलेक्स लॉजिक अॅरे ब्लॉक्स आणि अॅडॅप्टिव्ह लॉजिक मॉड्यूल्स, अॅजिलेक्स, लॉजिक अॅरे ब्लॉक्स आणि अॅडॅप्टिव्ह लॉजिक मॉड्यूल्स, अॅरे ब्लॉक्स आणि अॅडॅप्टिव्ह लॉजिक मॉड्यूल्स, अॅडॅप्टिव्ह लॉजिक मॉड्यूल्स, लॉजिक मॉड्यूल्स |